RRAM Crossbar Computing

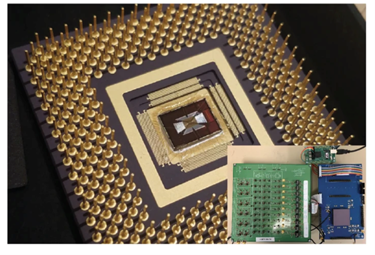

Memristors and memristor crossbar arrays have been widely studied for neuromorphic and other in-memory computing applications. For optimal system performance, however, it is essential to integrate memristor crossbars with peripheral and control circuitry. In a Nature cover paper we reported the first fully functional, hybrid memristor chip in which a passive crossbar array is directly integrated with custom-designed circuits, including a full set of mixed-signal interface blocks and a digital processor for reprogrammable computing. The memristor crossbar array enables online learning and forward and backward vector-matrix operations, while the integrated interface and control circuitry allow mapping of different algorithms on chip.

F. Cai, J. M. Correll, S. H. Lee , Y. Lim, V. Bothra, Z. Zhang, M. P. Flynn and W. D. Lu, "A Fully Integrated Reprogrammable Memristor– CMOS System for Efficient Multiply–accumulate Operations," in Nature Electronics, Vol. 2, July 15, 2019

J. M. Correll et al., "A Fully Integrated Reprogrammable CMOS-RRAM Compute-in-Memory Coprocessor for Neuromorphic Applications," in IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, vol. 6, no. 1, pp. 36-44, June 2020.

J. M. Correll et al., "A Fully Integrated Reprogrammable CMOS-RRAM Compute-in-Memory Coprocessor for Neuromorphic Applications," in IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, vol. 6, no. 1, pp. 36-44, June 2020.