Mixed-signal and Digital Spiking Neural Networks

The current revolution in machine learning is based on digital feed-forward CNN's comprising many layers. In contrast, the Locally Competitive Algorithm accomplishes similar tasks with fewer layers. LCA uses lateral inhibitory connections in addition to feed-forward connections in a spiking neural network. LCA relies on a biologically-inspired analog Leaky Integrate-and-Fire (LIF) neuron model, suggesting an efficient analog implementation.

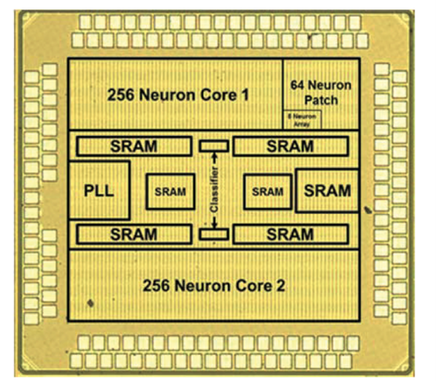

We introduced an analog neuron that is 3x smaller and consumes 7.5x less power than the comparable digital neuron, taking advantage of the sparse spiking behavior and low SNR requirement of LCA. Our internally-analog neuron presents fully digital I/O to facilitate efficient all-digital inter-neuron communication via address events (AE) and enables compatibility with a digital CAD flow.

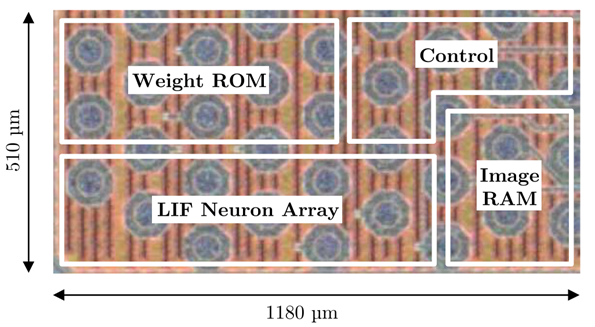

We also apply LCA to solve the heavy computing burden of compressive-sensing (CS) radar. CS radar circumvents the range-doppler uncertainty in radar, but requires conventional requires a very large amount of computation. One approach introduced by Herman and Strohmer for CS radar, assumes a time–frequency target space quantized into discrete atoms in both time and frequency dimensions. Our prototype solves the required sparse optimization with a recurrent spiking neural network and exhibits several innovations to address challenges in both enabling a large network size and adapting the network to evolve with complex-valued stimuli.

P. L. Brown, M. O'Shaughnessy, C. Rozell, J. Romberg, and M. P. Flynn, “A 17.8 MS/s Compressed Sensing Radar Accelerator Using a Spiking Neural Network,” IEEE Journal of Solid-State Circuits, In Press.

P. Brown, M. O' Shaugnessy, C. Rozell, J. Romberg, and M. P. Flynn, Zheng, H-W. Chen, R. Wang, M. P. Flynn, "A 17.8 MS/s Neural-Network Compressed Sensing Radar Processor in 16nm FinFET CMOS" 2020 IEEE Custom Integrated Circuits Conference (CICC), March 2020.

F. N. Buhler, P. Brown, J. Li, T. Chen, Z. Zhang and M. P. Flynn, “A 3.43TOPS/W 48.9pJ/Pixel 50.1nJ/Classification 512 Analog Neuron Sparse Coding Neural Network with On-Chip Learning and Classification in 40nm CMOS” 2017 IEEE Symposium on VLSI Circuits.

P. Brown, M. O' Shaugnessy, C. Rozell, J. Romberg, and M. P. Flynn, Zheng, H-W. Chen, R. Wang, M. P. Flynn, "A 17.8 MS/s Neural-Network Compressed Sensing Radar Processor in 16nm FinFET CMOS" 2020 IEEE Custom Integrated Circuits Conference (CICC), March 2020.

F. N. Buhler, P. Brown, J. Li, T. Chen, Z. Zhang and M. P. Flynn, “A 3.43TOPS/W 48.9pJ/Pixel 50.1nJ/Classification 512 Analog Neuron Sparse Coding Neural Network with On-Chip Learning and Classification in 40nm CMOS” 2017 IEEE Symposium on VLSI Circuits.