Continuous-Time and Bandpass Continuous-Time Delta-Sigma ADCs

Emerging wireless standards, such as 5G, require wide bandwidth (>100MHz), high dynamic range (DR) (>70dB), high SFDR (>80dB), analog to digital converters (ADCs). Continuous-time (CT) delta-sigma ADCs are very appealing for these applications because they simplify input filtering and provide an easy-to-drive signal input. Our work improves both the performance and efficiency of CT delta-sigma ADC. We also introduce new compelling new architectures for bandpass conversion and multi-band digitization.

One goal of our research is to expand the speed of CT delta-sigma ADCs. One bottleneck we have tackled is the speed limit due to data-weighted averaging (DWA), which is essential for high-resolution delta-sigma ADCs. We introduced the Time-Interleaved Reference Data- Weighted-Averaging (TI-RDWA) architecture to solve this speed limitation. Time-interleaving eliminates the reference voltage settling bottleneck, enabling DWA operation at 5GHz, while still achieving the benefits of first-order shaping of feedback DAC mismatch.

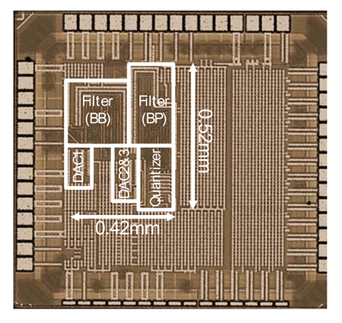

A bandpass continuous-time delta-sigma modulator (CTBPDSM) is a compelling solution for software-defined-radio (SDR). It allows great flexibility in the digital back-end and significantly reduces the receiver chain's complexity by combining several analog blocks into a single ADC. A single-opamp resonator circuit delivers high speed and excellent energy efficiency. Combined with bitstream processing, CTBPDSM ADCs revolutionize digital wireless beamforming. Multiband operation of CTBPDSM greatly simplifies channel aggregation in 4G and 5G wireless communication.

S. Jang, R. Lu, J. Jeong and M. P. Flynn, "A 1-GHz 16-Element Four-Beam True-Time-Delay Digital Beamformer," in IEEE Journal of Solid-State Circuits, February 2019.

J. Bell and M. P. Flynn, "A Simultaneous Multiband Continuous-Time Delta Sigma ADC With 90-MHz Aggregate Bandwidth in 40-nm CMOS," in IEEE Solid-State Circuits Letters, September 2019.

M. B. Dayanik, D. Weyer and M. P. Flynn “A 5GS/s 156MHz BW 70dB DR Continuous-Time Sigma-Delta Modulator with Time-Interleaved Reference Data-Weighted Averaging” 2017 IEEE Symposium on VLSI Circuits.

J. Jeong, N. Collins, and M. P. Flynn, "A 260 MHz IF Sampling Bit-Stream Processing Digital Beamformer with an Integrated Array of Continuous-Time Band-Pass ΔΣ Modulators," IEEE Journal of Solid-State Circuits, May 2016.

H. Chae and M.P. Flynn, “A 69dB SNDR, 25MHz BW, 800MS/s Continuous-time Bandpass ΔΣ Modulator Using a Duty-cycle-controlled DAC for Low Power and Reconfigurability,” IEEE Journal of Solid-State Circuits, March 2016.

J. Bell and M. P. Flynn, "A Simultaneous Multiband Continuous-Time Delta Sigma ADC With 90-MHz Aggregate Bandwidth in 40-nm CMOS," in IEEE Solid-State Circuits Letters, September 2019.

M. B. Dayanik, D. Weyer and M. P. Flynn “A 5GS/s 156MHz BW 70dB DR Continuous-Time Sigma-Delta Modulator with Time-Interleaved Reference Data-Weighted Averaging” 2017 IEEE Symposium on VLSI Circuits.

J. Jeong, N. Collins, and M. P. Flynn, "A 260 MHz IF Sampling Bit-Stream Processing Digital Beamformer with an Integrated Array of Continuous-Time Band-Pass ΔΣ Modulators," IEEE Journal of Solid-State Circuits, May 2016.

H. Chae and M.P. Flynn, “A 69dB SNDR, 25MHz BW, 800MS/s Continuous-time Bandpass ΔΣ Modulator Using a Duty-cycle-controlled DAC for Low Power and Reconfigurability,” IEEE Journal of Solid-State Circuits, March 2016.