Clock Generation, Radar Chirps Generation and PLLs

Accurate, low-noise clocks are essential for wireless communication, analog-digital conversion, and radar. Our work explores new mostly-digital PLLs architectures aided by analog-to-digital converters. These ADCs work as accurate phase detectors to enable digital signal processing within the PLL.

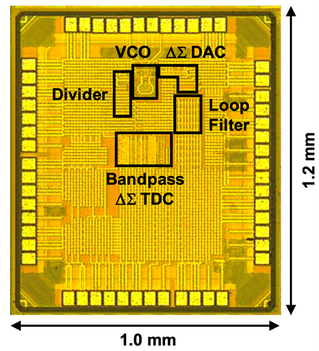

The development of self-driving cars has sparked a growing need for reliable automotive sensors. Among these sensor systems, frequency-modulated continuous-wave (FMCW) radar has emerged as a key technology. Phase locked loops (PLLs) are an effective tool for generating FMCW chirp waveforms and have been widely adopted for integrated circuit implementations. Although most high-frequency PLLs are implemented as analog PLLs, digital PLLs offer better reconfigurability and area efficiency. However, chirp synthesizer designs based on digital PLLs must contend with the limited resolution of conventional time-to-digital converters (TDCs). Our research investigates noise-shaping TDCs to measure phase. Noise shaping TDCs leverage the high resolution of a delta-sigma modulators to enable low phase noise and fast frequency settling in a single-loop digital mm-wave PLL.

M. B. Dayanik and M. P. Flynn, "Digital Fractional-N PLLs Based on a Continuous-Time Third-Order Noise-Shaping Time-to-Digital Converter for a 240-GHz FMCW Radar System," in IEEE Journal of Solid-State Circuits, March 2018.

D. Weyer, M. B. Dayanik, S. Jang and M. P. Flynn, "A 36.3-to-38.2GHz −216dBc/Hz2 40nm CMOS fractional-N FMCW chirp synthesizer PLL with a continuous-time bandpass delta-sigma time-to-digital converter," 2018 IEEE International Solid - State Circuits Conference, February 2018.

Y. Rajavi, M. M. Ghahramani, A. Khalili, A. Kavousian B. Kim, and M. P. Flynn, “A 48MHz Differential Crystal Oscillator with 168fs Jitter in 28nm CMOS” IEEE Journal of Solid-State Circuits, October 2017.

M. Batuhan Dayanik, N. Collins and M. P. Flynn, "A 28.5 – 33.5GHz Fractional-N PLL Using a 3rd Order Noise Shaping Time-to-Digital Converter with 176fs Resolution," European Solid-State Circuits Conference (ESSCIRC), September 2015.

M. M, Ghahramani, Y. Rajavi, A. Khalili, A. Kavousian,B. Kim, and M. P. Flynn, "A 192MHz Differential XO Based Frequency Quadrupler with Sub-Picosecond Jitter in 28nm CMOS," IEEE Radio Frequency Integrated Circuits Symposium (RFIC), June, 2015.

L. Li, M. A. Ferriss, and M. P. Flynn, "A 5.8GHz Digital Arbitrary Phase-Setting Type II PLL in 65nm CMOS with 2.25deg Resolution," Asia Solid-State Circuits Conference (ASSCC), November, 2012.

M. Ghahramani, M. Ferriss, and M. P. Flynn, "A 2.4GHz 2Mb/s digital PLL-based transmitter for 802.15.4 in 130nm CMOS," Radio Frequency Integrated Circuits Symposium (RFIC), 2011 IEEE, June , 2011.

M. Ferriss, D. Lin, and M. P. Flynn, "A Fractional-N PLL modulator with flexible direct digital phase modulation," IEEE Custom Integrated Circuits Conference (CICC), September, 2009.

M. Ferriss and M. P. Flynn, "A 14mW Fractional-N PLL modulator with a digital phase detector and frequency switching scheme," IEEE Journal of Solid-State Circuits, November 2008.

M. Ferriss and M. P. Flynn, "A 14mW Fractional-N PLL modulator with a novel digital phase detector and frequency switching scheme," IEEE International Solid State Circuits Conference (ISSCC), February , 2007.

D. Weyer, M. B. Dayanik, S. Jang and M. P. Flynn, "A 36.3-to-38.2GHz −216dBc/Hz2 40nm CMOS fractional-N FMCW chirp synthesizer PLL with a continuous-time bandpass delta-sigma time-to-digital converter," 2018 IEEE International Solid - State Circuits Conference, February 2018.

Y. Rajavi, M. M. Ghahramani, A. Khalili, A. Kavousian B. Kim, and M. P. Flynn, “A 48MHz Differential Crystal Oscillator with 168fs Jitter in 28nm CMOS” IEEE Journal of Solid-State Circuits, October 2017.

M. Batuhan Dayanik, N. Collins and M. P. Flynn, "A 28.5 – 33.5GHz Fractional-N PLL Using a 3rd Order Noise Shaping Time-to-Digital Converter with 176fs Resolution," European Solid-State Circuits Conference (ESSCIRC), September 2015.

M. M, Ghahramani, Y. Rajavi, A. Khalili, A. Kavousian,B. Kim, and M. P. Flynn, "A 192MHz Differential XO Based Frequency Quadrupler with Sub-Picosecond Jitter in 28nm CMOS," IEEE Radio Frequency Integrated Circuits Symposium (RFIC), June, 2015.

L. Li, M. A. Ferriss, and M. P. Flynn, "A 5.8GHz Digital Arbitrary Phase-Setting Type II PLL in 65nm CMOS with 2.25deg Resolution," Asia Solid-State Circuits Conference (ASSCC), November, 2012.

M. Ghahramani, M. Ferriss, and M. P. Flynn, "A 2.4GHz 2Mb/s digital PLL-based transmitter for 802.15.4 in 130nm CMOS," Radio Frequency Integrated Circuits Symposium (RFIC), 2011 IEEE, June , 2011.

M. Ferriss, D. Lin, and M. P. Flynn, "A Fractional-N PLL modulator with flexible direct digital phase modulation," IEEE Custom Integrated Circuits Conference (CICC), September, 2009.

M. Ferriss and M. P. Flynn, "A 14mW Fractional-N PLL modulator with a digital phase detector and frequency switching scheme," IEEE Journal of Solid-State Circuits, November 2008.

M. Ferriss and M. P. Flynn, "A 14mW Fractional-N PLL modulator with a novel digital phase detector and frequency switching scheme," IEEE International Solid State Circuits Conference (ISSCC), February , 2007.