# A Fully Self-Contained Logarithmic Closed-Loop Deep Brain Stimulation SoC With Wireless Telemetry and Wireless Power Management

Hyo-Gyuem Rhew, Jaehun Jeong, Jeffrey A. Fredenburg, *Student Member, IEEE*, Sunjay Dodani, Parag G. Patil, and Michael P. Flynn, *Senior Member, IEEE*

Abstract—Although closed-loop deep brain stimulation (DBS) promises treatment of many neurological disorders, an implantable system-on-chip (SoC) implementing an effective closed-loop DBS algorithm has not been demonstrated. This work introduces a logarithmic, closed-loop DBS system that detects and processes low-frequency brain field signals to control and adapt stimulation currents. The system records and processes neural signals with four low-noise neural amplifier (LNA) channels, a multiplexed logarithmic ADC, and two high-pass and two low-pass digital logarithmic filters. Logarithmic processing saves power and achieves high dynamic range. A logarithmic domain digital signal processor (DSP) and PI-controller controls eight current stimulator channels and enables closed-loop stimulation. An RF transceiver, a clock generator, and a power harvester are also included in the system to achieve a complete implantable SoC. The 4 mm<sup>2</sup> 180 nm CMOS prototype consumes a total of 468  $\mu$ W for recording and processing neural signals, for stimulation, and for two-way wireless communication.

Index Terms—Closed-loop deep brain stimulation (DBS), local field potential (LFP), log-domain DSP, logarithmic ADC, PI controller.

#### I. Introduction

D EEP-BRAIN stimulation (DBS) has provided remarkable therapeutic benefits for neurological disorders such as essential tremor and Parkinson's disease [1], [2]. However, despite the long history of DBS and more than a decade of research, the underlying principles of DBS and a mechanism for optimizing stimulation parameters remain elusive. Currently, visual symptoms are the most effective feedback indicator for the optimal selection of stimulation parameters, such as amplitude, pulse-width, and repetition rate. For each patient, there is a unique set of signal amplitudes, pulse-widths and repetition

Manuscript received May 29, 2014; accepted July 27, 2014. Date of publication August 28, 2014; date of current version September 22, 2014. This paper was approved by Associate Editor Ken Shepard. This work was supported by the Catalyst Foundation.

H.-G. Rhew is with Broadcom, Central Engineering, Irvine, CA 92612 USA (e-mail: hyoanty@gmail.com, hrhew@umich.edu).

J. Jeong, J. A. Fredenburg, P. G. Patil, and M. P. Flynn are with the Department of Electrical Engineering, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: jaehun@umcih.edu, fredenbu@umich.edu, pgpatil@med.umich.edu, jssc@eecs.umich.edu).

S. Dodani is with Medallia, San Francisco, CA, USA (e-mail: sunjay.dodani@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2014.2346779

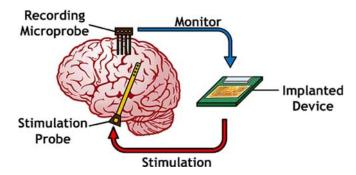

Fig. 1. Conceptual diagram of closed-loop DBS.

rates that are effective for treatment. With open-loop DBS systems, a post-surgery process called *programming* is necessary for the best results [3]. Initial programming takes 2–3 hours and thereafter the patient is observed for at least 1–2 hours to make fine adjustments. Programming is repeated frequently during the first 6 months and patients must visit a neurologist or a trained technician periodically to ensure the best treatment of symptoms as patient's condition changes over time.

Closed-loop DBS promises much simpler programming and also an easier and better patient experience. The principle of closed-loop DBS is shown in Fig. 1. It is believed that the best candidates for the closed-loop feedback signal are abnormal pattern changes in spike signals or changes in the local field potential (LFP) signals. Neural spike signals, also known as action potentials, have bandwidths ranging from 100 Hz to 10 kHz and amplitudes up to 500  $\mu$ V [4], while LFP signals have bandwidths from 1 Hz to 100 Hz and amplitudes up to 5 mV [5]. Among these, neural spike signals have been considered as a possible candidate for the feedback indicator. To this end, a biomedical multiprocessor system-on-chip (SoC) for closed-loop neuroprosthetic applications has been proposed [6]. This biomedical multiprocessor performs real-time spike-sorting through principal component analysis (PCA). Other work on a closed-loop biomedical system has developed an activity-dependent intracortical microstimulation SoC [7]. This SoC embeds a digital spike discrimination processor that triggers stimulation every time it captures a neural spike signal stronger than a preset threshold. Although the combination of spike sorting and PCA can disentangle spikes, this approach has some drawbacks such as the large power consumption

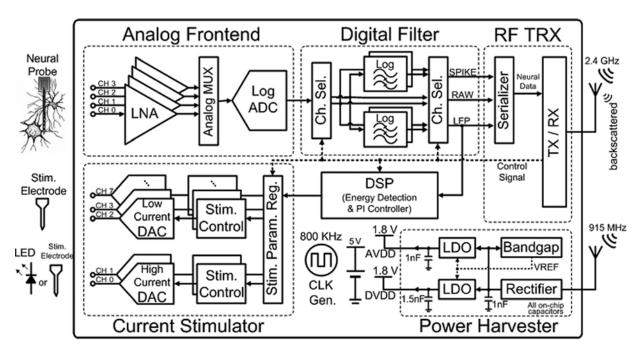

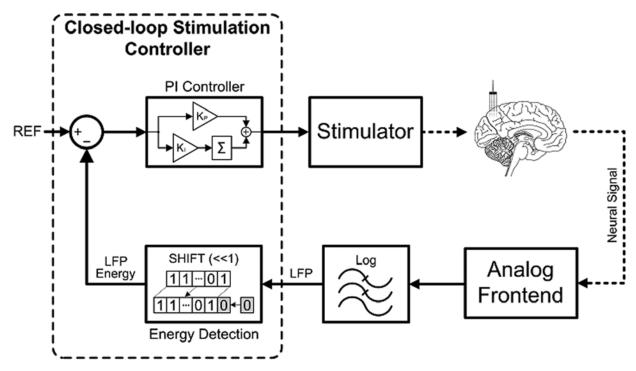

Fig. 2. Overall system block diagram of the proposed log-based closed-loop DBS system.

required for real-time computation [6] and a high sensitivity to stimulation artifacts [7]. Moreover, spike sorting and PCA require significant on-chip computation making wireless powered or long-term battery powered operation difficult.

Recently, features of the LFP signals, and in particular the energy of LFPs, have emerged as a more effective feedback indicator for setting and tuning DBS [8]. An implantable closed-loop microstimulator targeted for DBS therapy uses analog spectral analysis to extract features of the LFP signals [9]. The system incorporates a custom IC for recording and spectral analysis, an auxiliary microprocessor for extracting key bioelectrical signals, and an existing neurostimulator device. However, this system consists of several different ICs, and consumes a lot of power.

In this paper, we describe the first wirelessly-powered closed-loop DBS system-on-chip (SoC) with two-way wireless telemetry. A new closed-loop neural stimulation architecture exploits the logarithmic characteristic of neural signals, so that efficient log-domain digital signal processing extracts information for closed-loop feedback, allowing long-duration battery-powered operation or operation from harvested RF power. The 180 nm CMOS prototype incorporates low-noise neural amplifiers and a log-ADC to efficiently record both low-frequency LFP signals and high-frequency spike signals. A log-based DSP block determines the energy of the LFP signals digitized by the log-ADC. Based on analysis of LFP energy, as proposed in recent brain research [8], an on-chip closed-loop feedback path controls the stimulation channels. The prototype device is fully self-contained and in addition to the recording and stimulation functions it also incorporates energy recovery, voltage regulation and on-chip clock generation to enable a true single-chip solution. To broaden the utility of this system for research, the prototype IC also incorporates two-way telemetry as well as support for optical stimulation for optogenetic research.

### II. SYSTEM ARCHITECTURE OVERVIEW

The overall system architecture is shown in Fig. 2. We significantly improve energy efficiency by introducing a complete logarithmic domain neural recording and processing chain. We take advantage of the fact that neural signals, like many other natural signals, can be elegantly expressed in a logarithmic scale to reduce the bit resolution dictated by the dynamic range. Four band-pass low-noise neural amplifiers (LNAs) filter and amplify neural signals before these signals are multiplexed to a single 100kSample/s 8b logarithmic pipeline ADC [10]. Each LNA has a nominal pass-band gain of 54dB and a passband transition region slope of -40 dB/decade. The logarithmic DSP simultaneously processes the logarithmic-scale digital outputs of two recording channels. Logarithmic domain digital filtering saves power by replacing digital multiplication with simple addition. Similarly, the logarithmic DSP calculates LFP energy by performing simple 1 bit left-shifting instead of squaring. Uniquely, the on-chip DSP in this work also includes a programmable PI-controller that evaluates the LFP energy information to set the optimal stimulation amplitude. An advantage is that the closed-loop feedback is based on low-pass-filtered LFP signals, making the closed-loop DBS operation robust to high-frequency stimulation artifacts.

There are two different types of neurostimulation: voltage stimulation and current stimulation. Since the clinical efficacy of voltage stimulation can gradually decrease as the impedance of the implanted electrodes increases due to reactive tissue response [11], we employ current stimulation in this work because with current stimulation the injected charge is independent of the load impedance. Biphasic stimulation avoids tissue damage

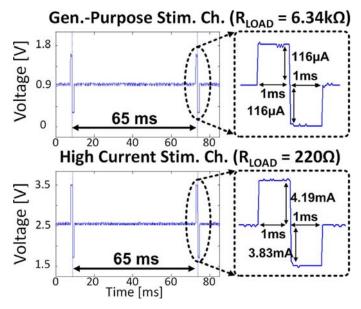

caused by residual charge. Stimulation parameters include the amplitude, the pulse width and the frequency (repetition rate) of stimulation current. Each parameter value is set with 6 bit resolution. As shown in Fig. 2, the stimulator consists of six 6b general-purpose (amplitude up to  $116~\mu A$ ) channels and two 6b high-current (amplitude up to 4.2~mA) stimulation channels. The high current driving capability of the current stimulator allows a LED to be powered and this extends the potential use of this DBS system to optogenetic applications.

The prototype device is wirelessly powered or can run from a battery if high current stimulation is required. Many biomedical systems are powered through low-frequency inductive coupling [12]–[14]. However, considering tissue absorption and antenna performance, recently, much higher frequencies (i.e., GHz) have been used to optimize power transmission [15]. We exploit higher frequency coupling to implement efficient power delivery and to reduce antenna size. The power management block recovers energy from a 915MHz carrier to power the entire system. The power management block is comprised of an RF-DC converter and two on-chip LDOs.

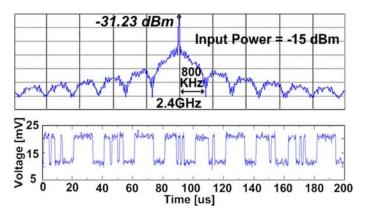

The self-contained single-chip system also incorporates a bandgap reference, bias circuitry and a low jitter clock generator. The jitter of the relaxation clock generator is low enough to support the ADC precision. The stimulation parameters can be directly set via a 2.4 GHz wireless downlink. In addition to the receiver, the device includes a power-efficient 800kbps backscatter RF transmitter that wirelessly communicates recorded LFP, spike or raw data to an external receiver.

### III. LOGARITHMIC SIGNAL RECORDING AND PROCESSING

### A. Logarithmic Analog-to-Digital Conversion

If we assume an N bit logarithmic ADC with an input voltage,  $V_{\rm IN}$ , a full scale input range,  $V_{\rm RANGE}$ , a log base, B, and output digital bits  $(b_{\rm N-1},\ b_{\rm N-2},\ldots,b_0)$ , then the transfer function of the ADC is given by [16]:

$$\left[2^{N} \cdot \log_{B} \left(B \cdot \frac{V_{in}}{V_{range}}\right)\right] = b_{N-1} 2^{N-1} + \dots + b_{0} \quad (1)$$

where [x] denotes the largest integer which is not larger than x. As the input amplitude increases, the quantization becomes coarser. LSB size is given by:

$$LSB = V_{range} \cdot \frac{B^{1/2^N} - 1}{B}.$$

(2)

The dynamic range (DR) is defined as the ratio of the input range to the smallest resolvable signal, and can be expressed as:

$$DR = \frac{V_{range}}{LSB} = \frac{B}{B^{1/2^N} - 1}.$$

(3)

From this equation, we see that DR increases as the base of logarithmic function, B, and the resolution, N, increase. A logarithmic ADC has a higher DR than a conventional linear ADC of the same bit resolution. We chose B=10 and N=7 for this work. An additional bit represents the sign of input, so that the overall ADC resolution is 8bits with one sign bit and seven magnitude bits. From (3) we see that a dynamic range of 54 dB is achieved. This dynamic range is high enough to capture all the information needed, considering the background noise of around 5  $\mu V_{\rm RMS}$  and practical maximum neural input amplitude of 1.2 mV.1

### B. Logarithmic Digital Signal Processing

The logarithmic DSP directly processes the logarithmic ADC output. Logarithmic arithmetic used in a digital filter in [17] consumes less power than a linear counterpart, while maintaining a high DR. Recently, a 32 bit processor core based on logarithmic arithmetic was developed for a low-power 3-D graphics system [18]. A logarithmic number system with an additional sign was proposed in early research [19] and this number system is adopted in this work. For a given DR requirement, fewer bits are needed for a logarithmic number system compared to a conventional linear number system. Furthermore, multiplication in linear-domain is equivalent to addition in logarithmic domain, so simple adders can replace power consuming multipliers. The elimination of multipliers and the reduction of number of required bits lead to lower total power consumption.

Addition in the log-domain is less straightforward than multiplication. The most popular way to implement addition in log-domain is a lookup table method that requires an adder and a ROM [20]. The ROM stores the values of  $\log(1+10^X)$  for different values of X. We use the look-up table method in our work because of its simplicity. The method is explained with the following equation:

$$\log(A+B) = \log\left(A\left(1+\frac{B}{A}\right)\right)$$

$$= \log A + \log\left(1+10^{\log B - \log A}\right) \tag{4}$$

where A and B are positive numbers. First,  $\log B - \log A$  is calculated and the value of  $\log(1+10^{\log B-\log A})$  is found from the ROM. Finally we get the value of  $\log(A+B)$  by adding  $\log A$  and  $\log(1+10^{\log B-\log A})$ .

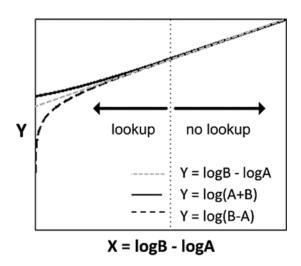

Addition can be further simplified when either A or B is much larger than the other. When  $\log B - \log A$  exceeds a certain value,  $1 + 10^{\log B - \log A}$  approximates to  $10^{\log B - \log A}$  and, as a result,  $\log A + \log(1 + 10^{\log B - \log A})$  approximates to  $\log B$ . The threshold for which this approximation is valid depends on the bit resolution of the digital number system. Fig. 3 visually explains the selective lookup table method. In the case where  $\log B - \log A$  is not larger than the threshold, the lookup table is needed to find the exact value of  $\log(1 + 10^{\log B - \log A})$ . In the case where B is much larger than A,  $\log(A + B)$  approximates to  $\log B$ . Thus, in the practical implementation, the difference,  $\log B - \log A$ , is calculated and compared to the threshold value to decide whether to use the lookup table or not.

<sup>1</sup>The neural signals we recorded from a rat's brain rarely exceed 1.2 mV, so we chose 1.2 mV as the maximum input amplitude for our system.

Fig. 3. Lookup table usage decision. (B > A > 0).

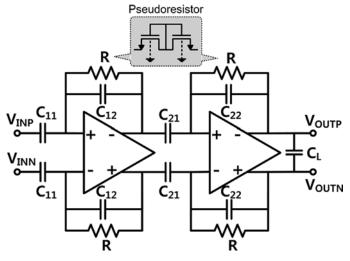

Fig. 4. Schematic of two-stage cascade band-pass LNA.

### IV. CIRCUIT IMPLEMENTATION

### A. Recording Front-end

Both the spikes and LFP signals carry useful information about the state of the brain [21]. Since the bandwidth and amplitude of these signals differ, few IC systems can simultaneously record both signals. Due to the very different amplitude ranges of spikes and LFPs, the LNAs must simultaneously exhibit a high dynamic range, good noise performance, and wide bandwidth. Given that the full scale input range of the ADC is 600 mV, as explained in Section III-B, and that the input amplitude of LFP signals is around 1 mV and rarely higher than 1.2 mV in our pre-recorded neural data, a pass-band gain of 500 (= 54 dB) is appropriate for the front-end LNA.

To achieve such a large closed-loop gain, a two-stage cascade structure is chosen for the LNA (Fig. 4). The two-stage structure consumes much less power for the same bandwidth compared to a conventional single stage amplifier. Also, since each stage in the two-stage LNA is a band-pass filter, the two-stage

structure suppresses out-of-band signals with a twice-steeper transition region slope compared to a single stage amplifier. Moreover, instead of implementing a feedback capacitance 500 times larger than input capacitance, the two-stage amplifier has a much smaller total capacitance. The first stage has a pass-band gain of 50, and the second stage has a gain of 10. This gain distribution means  $C_{12}=50\cdot C_{11}$  and  $C_{22}=10\cdot C_{21}$ , and, assuming  $C_{11}=C_{21}$ , the total feedback capacitance is  $60\cdot C_{11}$  instead of  $500\cdot C_{11}$  in the case of a single-stage amplifier. The larger gain of the first stage reduces the input-referred noise of the entire LNA due the second stage.

The first and second stage amplifiers are NMOS input folded cascode amplifiers. As shown in Fig. 4, a pseudoresistor comprised of two back-to-back diode-connected NMOS transistors emulates a high resistance, as large as  $10^{11}~\Omega$ . Compared to the configuration in [22], this configuration reduces the parasitic capacitance at both the input and output nodes of the amplifier because the gates of NMOS transistors are connected within the pseudoresistor. The simulated input-referred noise of the front-end LNA is 6.0  $\mu V_{\rm RMS}$ , which is comparable to the microelectrode noise and background cortical activity noise (5  $\mu V$ ) [23]. The nominal high-pass cutoff and low-pass cutoff frequencies are 1.4 Hz and 6 kHz, respectively, which ensures a wide enough pass-band to simultaneously record both LFP and spike signals.

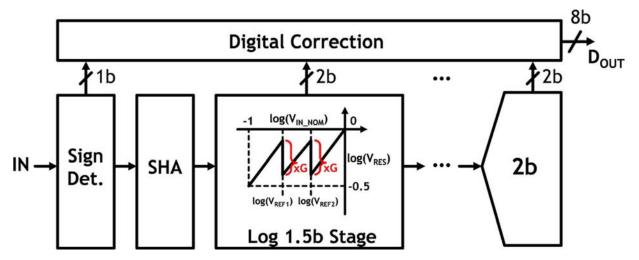

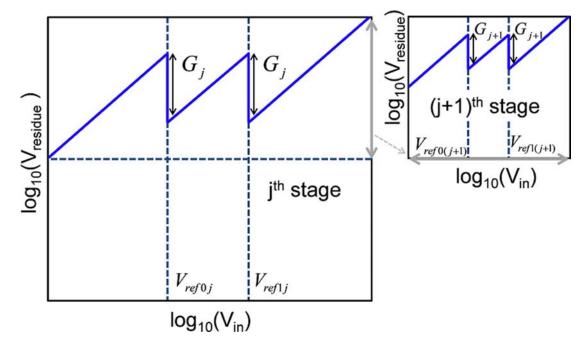

A simplified block diagram of the 8b pipeline log-ADC is shown in Fig. 5. First, the sign of input is determined. The input is inverted if negative because log functions can only operate on positive inputs. After sign detection, the input is processed through a SHA, five 1.5b log stages, and a 2b flash final stage. A digital correction block collects the digital bits and assembles an 8b output. A direct logarithmic implementation of the 1.5 bit per stage pipeline requires squaring to replace the multiplication-by-2 operation in a linear domain pipeline and conditional multiplication to replace the conditional addition or subtraction. Fig. 6 explains the conditional multiplication scheme and shows the scaling of the reference voltages and the multiplication gains for the different stages. To avoid analog squaring, the reference voltages for the comparators and the gain settings are scaled in order to achieve the same result as squaring the output of each 1.5 bit stage [24].

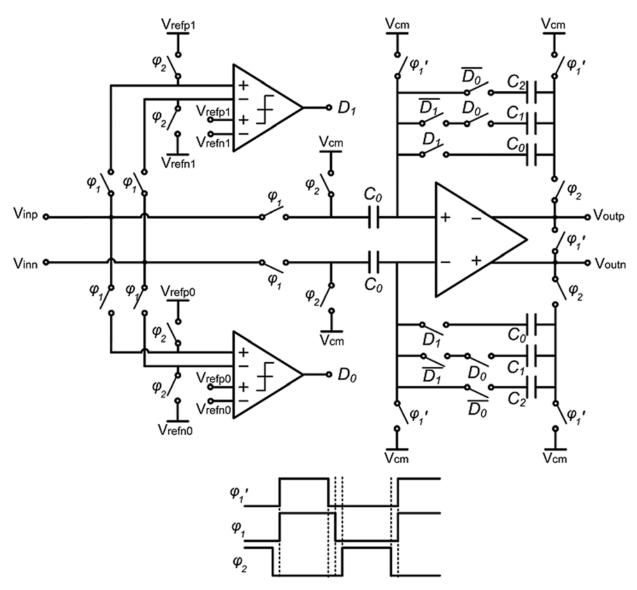

Fig. 7 shows one of the fully differential 1.5 bit stages of the logarithmic ADC. Three clock signals  $\varphi_1$ ,  $\varphi_1'$ , and  $\varphi_2$  control the operation of the 1.5 bit stages and implement bottom-plate sampling. When  $\varphi_1$  is high, the stage input is sampled and the output is reset. When  $\varphi_2$  is high, the two comparators decide the output bits and the residue is amplified with a gain that depends on the bit decision. The clock  $\varphi_1'$  is used for bottom plate sampling. A two-stage regenerative comparator is used for the 1.5 bit sub-ADCs. The size of the input pairs of the comparators is increased for progressive stages in the pipeline, as the mismatch requirement becomes stricter because the signal range decreases along the pipeline. Table I gives the reference voltage values and the gains for each stage.

Fig. 5. Block diagram of 8b logarithmic pipeline ADC.

Fig. 6. Scaling of reference voltages and conditional gains from  $j^{\rm th}$  stage to  $(j+1)^{\rm th}$  stage.

## B. Logarithmic Digital Filters and Closed-Loop Stimulation Controller

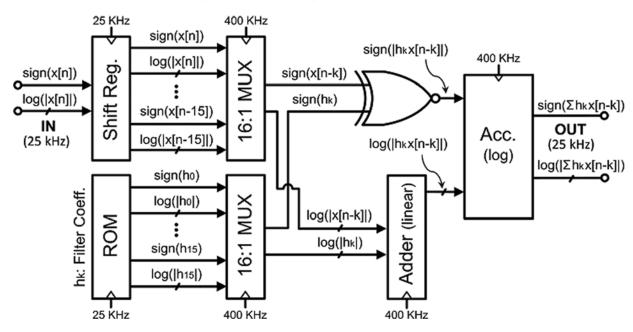

Log-domain digital filtering is introduced in this work to take advantage of the logarithmically encoded signals, and to directly process the log-scale digital output of the ADC. In the prototype system, two sets of high-pass and low-pass 15th order log-domain digital FIR filters separate spikes and LFPs in two channels (Fig. 2). The LPFs and HPFs have the same 3 dB cutoff frequency of 700 Hz. A block diagram of the 15th order digital log-filters is shown in Fig. 8. The digital log-filters receive a sign bit and the log-domain absolute value for each input signal. A ROM stores 16 filter coefficients. The high-pass and the low-pass filters are implemented in the same way but with different stored coefficients.

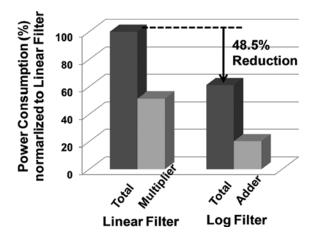

The digital circuitry reuses key blocks to minimize the area of the 15th order digital log-filters. A 400 kHz clock signal is derived from the 800 kHz system clock. Since the 400 kHz clock is 16 times faster than 25 kS/s data rate for each channel a single linear adder and a single logarithmic accumulator are reused 16 times for each 25 kS/s input. Compared to a conventional cascade FIR filter structure that has as many delay cells, multipliers, and adders as the order of the filter, this hardware reuse significantly reduces silicon area. A linear adder multiplies the absolute values of logarithmic input with the filter coefficients, while an XOR gate multiplies the sign with the sign coefficient. A log accumulator accumulates 16 filter products at 400 kHz and produces the final 25 kS/s filtered output. As illustrated in Fig. 9, the digital log-filters consume 48% less power than equivalent linear-filters thanks to the substitution of power-hungry multi-

Fig. 7. Simplified schematic of a logarithmic 1.5 bit stage.

TABLE I Voltage Reference and Gain Settings in the Logarithmic 8-Bit ADC With B=10.\* Vref2 is Needed for the 6th Stage Because a 2-Bit Flash ADC Needs Three Comparators

| Stage (j)    | 1 <sup>st</sup> | 2 <sup>nd</sup> | 3 <sup>rd</sup> | 4 <sup>th</sup> | 5 <sup>th</sup> | 6 <sup>th</sup> (2-bit<br>Flash) |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------------------|

| $V_{ref0j}$  | 142 mV          | 292 mV          | 419 mV          | 501 mV          | 548 mV          | 568 mV                           |

| $V_{reflj}$  | 253 mV          | 389 mV          | $484 \ mV$      | 539 mV          | 568 mV          | 579 mV                           |

| $V_{ref2j}*$ | -               | -               | -               | -               | -               | 589 mV                           |

| $G_{0j}$     | 3.162           | 1.778           | 1.334           | 1.155           | 1.075           | -                                |

| $G_{lj}$     | 1.778           | 1.334           | 1.155           | 1.075           | 1.037           | -                                |

| $G_{2j}$     | 1               | 1               | 1               | 1               | 1               | -                                |

pliers with adders and the aforementioned selective look-up table method.

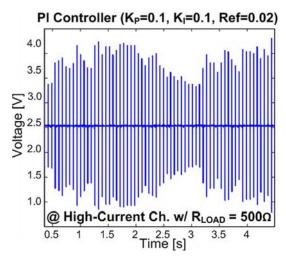

In this work, we introduce a closed-loop stimulation controller that includes a generic P.I. controller that optimizes the stimulation current in real-time. The P.I. controller adjusts the stimulation parameters based on the calculated LFP energy in

order to optimally suppress abnormal activity in the brain. A simplified signal flow diagram of the proposed closed-loop DBS is shown in Fig. 10. The log approach simplifies the calculation of LFP energy in the PI-controller. Instead of using squaring, the log-DSP determines the energy of the log-domain LFP signals with simple logical 1 bit left-shifting. The product of controller

### Logarithmic Digital FIR Filter

Fig. 8. Block diagram of digital logarithmic low-pass and high-pass filters.

Fig. 9. Simulated power consumption of a linear-domain filter and log-domain 10 bit FIR digital filters.

constants ( $K_P$  and  $K_I$ ) and the present input and integrated input are calculated in the log-domain through simple addition. The difference between input LFP energy and a reference energy value is calculated by the lookup table method. Using an accumulator and a logarithmic adder, the P.I. controller generates a final output and this output sets the current amplitude in real time.

### C. Current Stimulator

Current stimulation is selected for this work because a good current mode stimulator injects a constant charge into tissue, irrespective of fluctuations of load impedance. Biphasic stimulation is implemented to avoid tissue damage caused by residual charge. Programmable stimulation parameters include amplitude, pulse width and stimulating frequency (repetition rate or period) of stimulation current. The amplitude value is stored to 6 bit precision.

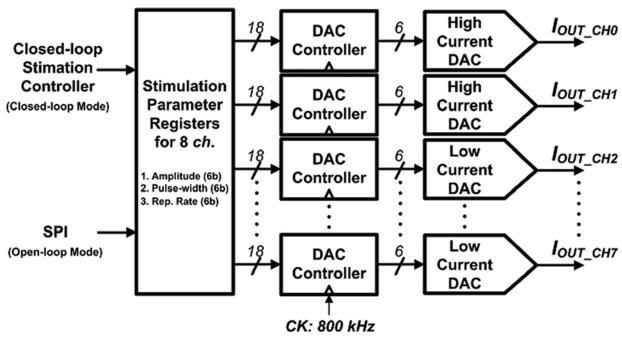

Fig. 11 shows a block diagram of the prototype 8-channel current stimulator. The current stimulator is comprised of three parts: eight 6 bit current steering DACs, dedicated DAC controllers for each DAC, and stimulation parameter registers. Stimulation parameters are either determined by the closed-loop stimulation controller in closed-loop operation or set directly by the user in open-loop mode through an SPI interface or through the RF receiver. The DAC controllers configure the current DACs to generate biphasic current stimulation with the amplitude, pulse-width and repetition rate stored in the registers. To support a variety of stimulation probes, six DACs are designed to drive currents up to 116  $\mu$ A, while the two other DACs can drive up to 4.2 mA. The high current channels can drive miniature LEDs for optogenetic applications as well as low impedance DBS probes. Because of the high current drive capability, the high current DACs are designed to run from a 5 V supply while the other DACs are powered from the main power management block. Operating from a 5 V supply, a current up to 3.3 mA can be supplied to a DBS probe (impedance range of  $473 \pm 159 \Omega$  [25]). Since the DAC controller operates from a 1.8 V supply voltage, level shifter circuits interface between the controller and the high current DACs. A triple-cascode current-steering DAC structure enhances the output impedance of both the general and the high current DACs to improve linearity. The ranges of stimulation parameters are summarized in Table II.

### D. RF Telemetry

In this work, a low-power backscatter based RF transceiver communicates to an external device. The power-efficient backscatter RF transmitter communicates recorded LFP, spike or raw data wirelessly to an external receiver at a data rate of 800 kbps. The RF transceiver consumes only 5  $\mu$ W from a

Fig. 10. Block diagram of the proposed closed-loop stimulation that uses LFP energy information as a feedback indicator.

Fig. 11. Block diagram of 8-channel current stimulator.

TABLE II

SUMMARY OF RANGES OF STIMULATION PARAMETERS

|                     | Amplitude      | Pulse-width | Period |

|---------------------|----------------|-------------|--------|

| High-current DAC    | $0 - 4.2 \ mA$ | 1 ms        | 65 ms  |

| General-purpose DAC | $0-116~\mu A$  | 1 ms        | 65 ms  |

1.8 V supply in transmit mode. Recently, backscatter communication has been used for implanted systems [26], [27].

In RFID applications where there is no dedicated power source, backscatter communication is attractive because of its

Fig. 12. Schematic of full-wave rectifier that generates unregulated  $V_{DD}$  of 2.2 V from a 915 MHz carrier.

TABLE III

PASS TRANSISTOR DIMENSION AND LOAD CAPACITANCE OF LDOS

|                 | Pass transistor dimension | Load capacitance |  |

|-----------------|---------------------------|------------------|--|

|                 | (W/L)                     | $(C_L)$          |  |

| LDO for Digital | 40μm / 180nm              | 1.5 nF           |  |

| LDO for Analog  | 20μm / 200nm              | 1.0 <i>nF</i>    |  |

extremely low power consumption and the simplicity of the transmitter design [28]. The backscatter transmitter consists simply of buffers and a switched transistor for impedance modulation. The impedance connected to the antenna changes depending on the transmitter input because the switched transistor changes the load.

### E. Power Management

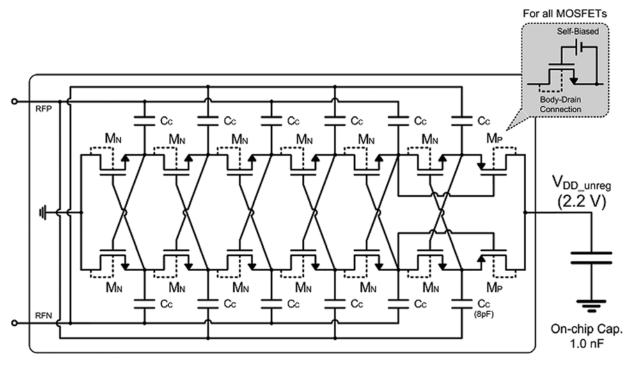

Wireless power delivery has many advantages for implantable devices including the elimination of a battery inside a human body. In this work, we implement a power management block comprised of a highly efficient RF-DC converter, two LDOs, and a bandgap reference circuit. The power management block generates 1.8 V from a 915 MHz carrier to power the entire DBS system. The high-current DACs require a 5 V battery.

A schematic of the RF-DC converter is illustrated in Fig. 12. A full-wave, self-threshold-compensated rectifier is chosen for its high power conversion efficiency [29]. At every phase, one half of the rectifier delivers charge to the on-chip capacitor. However, in an improvement over [29], here the body of each FET is tied to the drain for both lower on-resistance and less reverse-bias leakage. The rectifier generates an unregulated  $\rm V_{\rm DD}$  of 2.2 V and charges a 1 nF on-chip capacitor. The prototype

TABLE IV

POWER BREAKDOWN OF THE PROTOTYPE SYSTEM

| Part                                     | Power<br>Consumption    | Condition                                                                |  |

|------------------------------------------|-------------------------|--------------------------------------------------------------------------|--|

| LNA                                      | $16\mu W/\text{ch}$ .   | -                                                                        |  |

| Log-ADC                                  | $180 \mu W$             | -                                                                        |  |

| High-Current<br>Stimulation Ch.          | $62\mu A/\mathrm{ch}$ . | 4.2 mA amplitude, 1 ms pulsewidth, 15.4 Hz repetition rate.              |  |

| Low-Current<br>Stimulation Ch.           | 3 <i>μA</i> /ch.        | 116 µA amplitude, 1 ms pulsewidth<br>15.4 Hz repetition rate.            |  |

| Digital<br>(Filters+Stim.<br>Controller) | $138\mu W$              | All four filters (two LPFs and two<br>HPFs) are active.                  |  |

| RF Transceiver<br>(TX/RX)                | $5\mu W/4.6\mu W$       | One of TX and RX active at a time.                                       |  |

| Clock Generator                          | $60\mu W$               | 800 kHz clock output.                                                    |  |

| Total                                    | 468μW                   | All 6 general-purpose stimulators are active with 116 $\mu A$ amplitude. |  |

RF-DC converter exhibits a power conversion efficiency of 52% when the load current is 350  $\mu$ A.

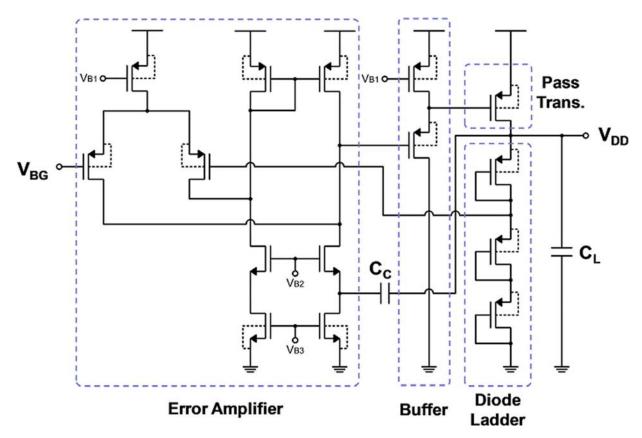

A schematic of the LDO that generates the supplies for the analog and the digital domains is shown in Fig. 13. The LDO consists of a folded cascode amplifier as an error amplifier, a

Fig. 13. An LDO generates a supply voltage for analog and digital domains.

Fig. 14. Clock generator.

buffer, and a pass transistor with a diode ladder and a load capacitor. To minimize power consumption a diode ladder instead of a resistor ladder sets the supply voltage values. The LDO loop is closed by connecting the output node in the diode divider ladder to the negative input node of the error amplifier. A bandgap reference voltage,  $V_{\rm BG}$ , functions as the reference input to the opamp. The pass transistor dimensions and the load capacitance values for the LDOs are given in Table III. A stack of MOSCAP, MOMCAP, and MiMCAP is used in the empty areas in the system to maximize the capacitor density. Also,

MOMCAP and MiMCAP are stacked on top of the digital circuitry for the same purpose. The pass transistor of the digital domain LDO is larger than that of the analog domain LDO for better transient performance required to handle digital supply spikes. The LDOs are fully implemented on-chip and require no external passive components.

### F. Clock Generator

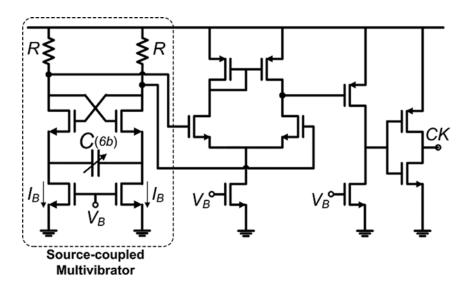

For stand-alone operation, the system needs a low-power on-chip generated clock signal. In this work, a source-coupled

TABLE V

PROTOTYPE PERFORMANCES SUMMARY

| Analog Front-end                                |                                     |  |  |  |

|-------------------------------------------------|-------------------------------------|--|--|--|

| LNA Gain                                        | 54 <i>dB</i>                        |  |  |  |

| LNA 3dB Passband                                | 0.64 <i>Hz</i> − 6 <i>kHz</i>       |  |  |  |

| Input Referred RMS Noise                        | $6.3  \mu V_{RMS}$                  |  |  |  |

| Noise Efficiency Factor (NEF)                   | 3.76                                |  |  |  |

| Logarithmic ADC Sampling Rate                   | 100 kSample/s                       |  |  |  |

| Analog Front-end Max DNL/INL                    | 0.82 <i>LSB</i> / 0.89 <i>LSB</i>   |  |  |  |

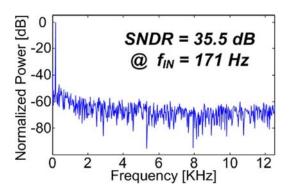

| Analog Front-end SNDR                           | 35.5 dB @ 170 Hz                    |  |  |  |

| Analog Front-end Power Consumption              | 245 μW                              |  |  |  |

| Current Stimulator                              |                                     |  |  |  |

| Maximum Current of High/Low Current DAC         | $\pm 4.18 \ mA \ / \pm 116 \ \mu A$ |  |  |  |

| Charge Unbalance of High/Low Current DAC        | < 9% / < 0.1%                       |  |  |  |

| Amplitude Resolution                            | 6-bit                               |  |  |  |

| Repetition Rate                                 | 15.4 Hz                             |  |  |  |

| Pulse Width                                     | 1 ms                                |  |  |  |

| Digital Filters + Stimulator Controller         |                                     |  |  |  |

| Clock Frequency                                 | 400 kHz                             |  |  |  |

| 3dB Cutoff Frequency of LPF / HPF               | 700 Hz / 700 Hz                     |  |  |  |

| Power Consumption                               | 138 μW                              |  |  |  |

| RF-DC Converter                                 |                                     |  |  |  |

| Carrier Frequency for Power Harvesting          | 915 MHz                             |  |  |  |

| Simulated Rectifier Power Conversion Efficiency | 52% @ I <sub>Load</sub> = 350 μA    |  |  |  |

| RF Transceiver                                  | •                                   |  |  |  |

| Communication Scheme of TX / RX                 | Backscatter / PWM                   |  |  |  |

| Carrier Frequency for RF Communication          | 2.4 <i>GHz</i>                      |  |  |  |

| Data Rate TX / RX                               | 800 kbps / 100 kbps                 |  |  |  |

| Power Consumption TX / RX                       | $5 \mu W / 4.6 \mu W$               |  |  |  |

| Clock Generator                                 |                                     |  |  |  |

| Output Frequency                                | 800 <i>kHz</i>                      |  |  |  |

| Simulated Cycle Jitter                          | 176 <i>p</i> s                      |  |  |  |

| Power Consumption                               | 60 μW                               |  |  |  |

| Total Power Consumption                         | 468μW                               |  |  |  |

| Technology                                      | 180nm 1P6M CMOS                     |  |  |  |

| Die Size (excluding pads)                       | 2 x 2 mm <sup>2</sup>               |  |  |  |

multivibrator generates an 800 kHz on-chip clock signal for the entire system. Fig. 14 shows a schematic of the clock generator. To maintain an ideal ADC effective resolution considering jitter above 10 bits, the clock generator is designed to achieve a cycle jitter of 176 ps while consuming only 60  $\mu W$  from 1.8 V supply and occupying only 20  $\times$  20  $\mu m^2$ . In normal operation, the capacitor C is always being charged by one of the source-coupled NMOSs. As the  $V_{\rm GS}$  of the switch becomes smaller than the threshold voltage because of the accumulated charge on C, the closed switch turns off and the open switch turns on. The current flow path is changed and the direction of charge accumulation on the capacitor is reversed. This process repeats and generates a periodically alternating output. The

jitter performance of the multivibrator improves inversely to the bias current as the uncertainty of switching instant becomes smaller with larger current. An open-loop two-stage amplifier and an inverter follow the source-coupled multivibrator to generate a rail-to-rail square wave from the small amplitude output of the source-coupled multivibrator. In addition, a 6 bit digitally controlled capacitor array allows an accurate 800 kHz output even with significant process variation.

### V. PROTOTYPE AND MEASUREMENTS

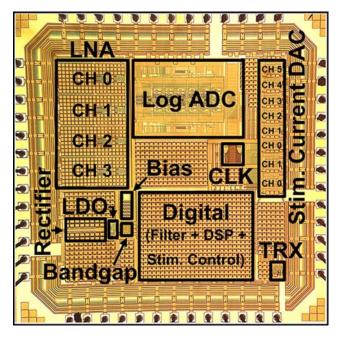

The prototype logarithmic closed-loop DBS SoC is fabricated in 180 nm CMOS. Fig. 15 shows a die micrograph of the

TABLE VI

PERFORMANCE COMPARISON WITH OTHER RECENT WORKS

|                               | This work                                                     | [26]              | [13]                   | [7]                     |

|-------------------------------|---------------------------------------------------------------|-------------------|------------------------|-------------------------|

| Recording Front-End           | Yes                                                           | Yes               | No                     | Yes                     |

| Number of channels            | 4                                                             | 1                 |                        | 8                       |

| AC Gain [dB]                  | 54                                                            | 49                |                        | 60                      |

| Low cutoff freq [Hz]          | 0.64                                                          | 100               |                        | 1.1 - 525               |

| High cutoff freq [KHz]        | 6                                                             | 2.5 - 6.2         |                        | 5.1 - 12                |

| ADC type                      | Pipeline (log)                                                | SAR               |                        | SAR                     |

| ADC resolution [bit]          | 8                                                             | 8                 |                        | 10                      |

| Sample rate [KS/s]            | 100                                                           | 80                |                        | 35.7                    |

| DNL / INL [LSB]               | < 0.82 / 0.84                                                 |                   |                        | < 0.8 / 0.8             |

| SNDR [dB]                     | 35.5                                                          |                   |                        | 42.18                   |

| Power [µW/channel]            | 61.25                                                         |                   |                        | 32.8                    |

| DSP                           | Yes                                                           | No                | No                     | Yes                     |

| Operation                     | Digital LPF/HPF,<br>LFP energy<br>Detection, PI<br>controller |                   |                        | Spike<br>discrimination |

| Power [µW]                    | 138                                                           |                   |                        | 12.4                    |

| Stimulating Back-End          | Yes                                                           | No                | Yes                    | Yes                     |

| Number of channels            | 2 + 8                                                         |                   | 100                    | 8                       |

| Max current [A]               | 4100μ / 116μ                                                  |                   | 600μ                   | 94.5μ                   |

| DAC resolution [bit]          | 6                                                             |                   | 4                      | 6                       |

| Transmitter                   | Yes                                                           | Yes               | No                     | Yes                     |

| Type                          | Backscatter                                                   | Backscatter       |                        | FSK                     |

| Frequency [MHz]               | 2400                                                          |                   |                        | 433                     |

| Data rate [kbps]              | 800                                                           | 150~800           |                        |                         |

| Power [µW]                    | 5                                                             |                   |                        | 200                     |

| Oscillator                    | Yes                                                           | Yes               | No                     | Yes                     |

| Output frequency [KHz]        | 800                                                           | 1200 - 6400       |                        | 1000                    |

| Power [µW]                    | 60                                                            |                   |                        | 20.8                    |

|                               |                                                               |                   |                        |                         |

| Power supply                  | RF-DC<br>(915MHz)<br>5V battery                               | RF-DC<br>(915MHz) | Inductive<br>(1-10MHz) | 1.5V battery            |

| Technology [µm]               | 0.18                                                          | 0.13              | 1.2                    | 0.35                    |

| Total area [mm <sup>2</sup> ] | 4                                                             | 1.54              | 21.62                  | 10.9                    |

prototype system. The total system (excluding I/O pads) occupies  $2 \times 2 \text{ mm}^2$ .

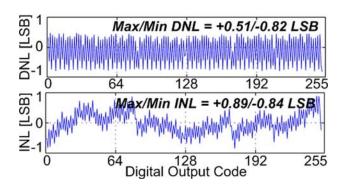

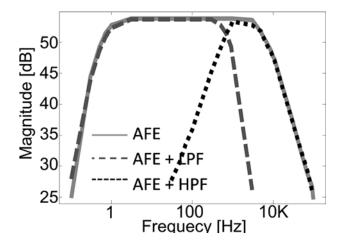

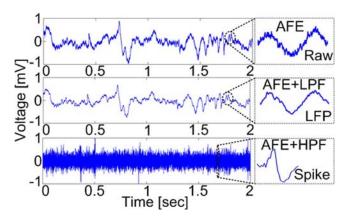

The prototype system is powered by a 915 MHz signal in a wirelessly powered mode, when Performance of the prototype system is measured. A 5 V battery is used only when high-current stimulators are used. The DNL/INL and output spectrum of the analog frontend (4 LNA channels and log-ADC combined) are measured with an input signal of 1.2 mV amplitude applied. The measured DNL and INL are shown in Figs. 16 and 17, respectively. The maximum DNL/INL are 0.82 LSB/0.89 LSB, and the maximum measured SNDR is 35.5 dB and the ENOB is 5.6 bit accordingly. A 10b dynamic range is achieved with the 8b logarithmic ADC with some trade-off in SNDR because of the log operation [10]. Fig. 18 shows the measured frequency response of the recording path (analog front-end and digital log-filters combined) when an input signal with amplitude of

1.2 mV is swept in frequency. The LNAs achieve a measured gain of 54 dB over a pass-band from 0.64 Hz to 6 kHz. Both the low-pass and high-pass digital filters have a 3 dB cutoff frequency of 700 Hz. Measured raw, LFP and spike recordings of a pre-recorded rat-brain neural signal recorded by the prototype are also shown in Fig. 19. These results clearly demonstrate that the log-scale recording path records neural signals in the frequency range of interest.

Fig. 20 shows measurements of stimulation current pulse trains in open-loop mode, with the current amplitudes set manually to the maximum amplitudes of  $116~\mu A$  and 4.19~m A for the general-purpose and high-current stimulation currents, respectively. Fig. 21 shows a measurement of the stimulation current in closed-loop mode. The stimulation current changes automatically in real-time and the variation of the current depends on the P.I. constants, reference energy value, and

Fig. 15. Die micrograph of the prototype logarithmic closed-loop DBS system.

Fig. 16. Measured DNL and INL of the designed analog front-end (4  $- {\rm ch.LNAs} + \log - {\rm ADC}).$

Fig. 17. Measured output spectrum of the designed analog front-end (4 – ch.LNAs +  $\log$  –ADC).

the energy of input LFP signals. The P.I. constants and the reference value can be adjusted to further enhance the efficacy of closed-loop DBS treatment. As shown in Fig. 21, the prototype DBS system clearly demonstrates closed-loop stimulation based on LFP energy information.

Fig. 22 shows the measured output spectrum and transmitted bit stream of the backscatter transmitter. Backscatter modula-

Fig. 18. Measured frequency response of the recording path (analog front-end + digital log-filters).

Fig. 19. Recorded transient output of the recording path (analog front-end + digital log-filters) with a pre-recorded neural signal from a rodent's brain applied as input to the system.

Fig. 20. Measured stimulation current waveforms of general-purpose (top) and high-current stimulation channels (bottom) with 6.23 k $\Omega$  and 220  $\Omega$  resistor loads, respectively.

tion is exploited in the transmitter to minimize power consumption, achieving an energy consumption of 6.25 pJ/b.

Fig. 21. Measured stimulation current waveforms of a high-current stimulation channel in closed-loop mode using LFP energy detection with a  $500~\Omega$  resistor load.

Fig. 22. Measured output spectrum of the backscatter transmitter and recovered data bit-stream from the backscatter transmitter after down-mixing with 2.4 GHz carrier.

The power consumption of each block is shown in Table IV. The measured total power consumption of the system is 468  $\mu$ W. The overall system performance is summarized in Table V. Table VI compares the system performance of this work with that of other recent works.

### VI. CONCLUSIONS

This work introduces the first fully-self-contained wirelessly-powered closed-loop DBS SoC. The closed-loop DBS system analyzes LFP energy information to set the optimal stimulation current amplitude. Log-domain digitization and signal processing improves energy efficiency, allowing wirelessly-powered operation. High-current stimulators facilitate optogenetic and DBS applications. A two-way wireless interface adds to the flexibility of the device.

### REFERENCES

- [1] PL Gildenberg, "Evolution of neuromodulation," *Stereotactactic and Functional Neurosurgery*, vol. 83, no. 2–3, pp. 71–79, Jul. 2005.

- 2] M. L. Kringelbach, N. Jenkinson, S. L. Owen, and T. Z. Aziz, "Translational principles of deep brain stimulation," *Nature Reviews Neuroscience*, vol. 8, no. 8, pp. 623–635, Aug. 2007.

- [3] W. Thevathasan and R. Gragory, "Deep brain stimulation formovement disorders," *Practical Neurology*, vol. 10, pp. 16–26, Feb. 2010.

- [4] K. Najafi and K. D. Wise, "An implantable multielectrode array with on-chip signal processing," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 1035–1044, Dec. 1986.

- [5] A. C. M. v. Rijn, A. Peper, and C. A. Grimbergen, "High-quality recording of bioelectric events," *Med. Biol. Eng. Comput.*, vol. 28, pp. 389–397, 1990.

- [6] T. Chen, K. Chen, Z. Yang, K. Cockerham, and W. Liu, "A biomedical multiprocessor SoC for closed-loop neuroprosthetic applications," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2009, pp. 434–435.

- [7] M. Azin, D. Guggenmos, S. Barbay, R. Nudo, and P. Mohseni, "A battery-powered activity-dependent intracortical microstimulation IC for brain-machine-brain interface," *IEEE J. Solid-State Circuits*, vol. 46, pp. 731–745, Apr. 2011.

- [8] F. Yoshida, I. Martinez-Torres, A. Pogosyan, E. Holl, E. Petersen, C. Chen, T. Foltynie, P. Limousin, L. Zrinzo, M. Hariz, and P. Brown, "Value of subthalamic nucleus local field potentials recordings in predicting stimulation parameters for deep brain stimulation in Parkinson's disease," J. Neurology, Neurosurgery and Psychiatry, vol. 81, no. 8, pp. 885–889, Aug. 2010.

- [9] A.-T. Avestruz, W. Santa, D. Carlson, R. Jensen, S. Stanslaski, A. Helfenstine, and T. Denison, "A 5 μW/channel spectral analysis IC for chronic bidirectional brain-machine interfaces," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 3006–3024, Dec. 2008.

- [10] J. Lee, J. Kang, S. Park, J. Seo, J. Anders, J. Guilhereme, and M. P. Flynn, "A 2.5 mW 80 dB DR 36 dB SNDR 22 MS/s logarithmic pipeline ADC," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2755–2765, Oct. 2009.

- [11] V. S. Polikova, P. A. Trescob, and W. M. Reicherta, "Response of brain tissue to chronically implanted neural electrodes," *J. Neurosci. Methods*, vol. 148, pp. 1–18, Oct. 2005.

- [12] T. Akin, K. Najafi, and R. M. Bradley, "A wireless implantable multichannel digital neural recording system for a micromachined sieve electrode," *IEEE J. Solid-State Circuits*, vol. 33, no. 1, pp. 109–118, Jan. 1998.

- [13] W. Liu, K. Vichienchom, M. Clements, S. C. DeMarco, C. Hughes, E. McGucken, M. S. Humayun, E. d. Juan, J. D. Weiland, and R. Greenberg, "A neuro-stimulus chip with telemetry unit for retinal prosthetic device," *IEEE J. Solid-State Circuits*, vol. 35, no. 10, pp. 1487–1497, Oct. 2000.

- [14] K. F. E. Lee, "A timing controlled AC-DC converter for biomedical implants," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2010, pp. 128–129.

- [15] A. S. Y. Poon, S. O'Driscoll, and T. H. Meng, "Optimal frequency for wireless power transmission into dispersive tissue," *IEEE Trans. Antennas Propagat.*, vol. 58, pp. 1739–1750, May 2010.

- [16] J. Lee, J. Kang, S. Park, J. Seo, J. Anders, J. Guilhereme, and M. P. Flynn, "A 2.5 mW 80 dB DR 36 dB SNDR 22 MS/s logarithmic pipeline ADC," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2755–2765, Oct. 2009.

- [17] N. G. Kingsbury and P. J. W. Rayner, "Digital filtering using logarithmic arithmetic," *IEEE Electron. Lett.*, vol. 7, pp. 56–58, Jan. 1971.

- [18] B.-G. Nam and H.-J. Yoo, "An embedded stream processor core based on logarithmic arithmetic for a low-power 3-D graphic soe," *IEEE J. Solid-State Circuits*, vol. 44, no. 5, pp. 1544–1570, May 2009.

- [19] E. E. Swartzlander and A. G. Alexopoulos, "The sign/logarithm number system," *IEEE Trans. Comput.*, vol. C-24, pp. 1238–1242, Dec. 1975.

- [20] L. K. Yu and D. M. Lewis, "A 30-b integrated logarithmic number system processor," *IEEE J. Solid-State Circuits*, vol. 26, no. 10, pp. 1433–1440, Oct. 1991.

- [21] T. C. Marzullo, J. R. Dudley, C. R. Miller, L. Trejo, and D. R. Kipke, "Spikes, local field potentials, and electrocorticogram characterization during motor learning in rats for brain machine interface tasks," in *IEEE 27th Annu. Int. Conf. Eng. Medicine and Biology Soc.*, Sep. 6, 2005.

- [22] J. Lee, H.-G. Rhew, D. R. Kipke, and M. P. Flynn, "A 64-channel programmable closed-loop neurostimulator with 8-channel neural amplifier and logarithmic ADC," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1935–1945, Sep. 2010.

- [23] K. S. Guillory and R. A. Normann, "A 100-channel system for real time detection and storage of extracellular spike waveforms," *J. Neurosci. Methods*, vol. 91, 1999.

- [24] J. Guilherme and J. Franca, "New CMOS logarithmic A/D converters employing pipeline and algorithmic architecture," in *Proc. IEEE Int. Symp. Circuits and Systems*, 1995, vol. 1, pp. 529–532.

- [25] X. F. Wei and W. M. Grill, "Impedance characteristics of deep brain stimulation electrodes *in vitro* and *in vivo*," *J Neural Eng.*, vol. 6, no. 4, p. 046008, Aug. 2009.

- [26] Z. Xiao, C. Tang, C. Dougherty, and R. Bashirullah, "A 20 μW neural recording tag with supply-current modulated AFE in 0.13 μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2010, pp. 122–123.

- [27] R. Harrison, H. Fotowat, R. Chan, R. J. Kier, R. Olberg, A. Leonardo, and F. Gabbiani, "Wireless neural/EMG telemetry systems for small freely moving animals," *IEEE Trans. Biomed. Circuits Syst.*, vol. 5, no. 2, pp. 103–111, Apr. 2011.

- [28] M. L. Kringelbach, N. Jenkinson, S. L. Owen, and T. Z. Aziz, "Translational principles of deep brain stimulation," *Nature Reviews Neuroscience*, vol. 8, no. 8, pp. 623–635, Aug. 2007.

- [29] G. Papotto, F. Carrara, and G. Palmisano, "A 90-nm CMOS threshold-compensated RF energy harvester," *IEEE J. Solid-State Circuits*, vol. 46, no. 9, pp. 1985–1997, Sep. 2011.

**Hyo-Gyuem Rhew** received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 2006. He received the M.S. and Ph.D. degrees, both in electrical engineering, from University of Michigan, Ann Arbor, MI, in 2009 and in 2012, respectively.

He held internship positions with MediaTek in 2008 and with Intel in 2012. He is now with the Central Engineering group of Broadcom, Irvine, CA, USA. His interests include SERDES and high-speed ADC/DAC design.

Dr. Rhew received a Samsung Scholarship (from 2006 to 2010) and was a co-recipient of the Outstanding Student Designer Award from Analog Devices, Inc. in 2008.

**Jaehun Jeong** received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea in 2006, and the M.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2011, where he is currently pursuing the Ph.D. degree.

His research interests include analog/mixed circuits for multiplier-less digital implementation.

Mr. Jeong received a scholarship from the Korea Foundation for Advanced Studies (KFAS) in 2009.

**Jeffrey A. Fredenburg** (S'08) received the B.S.E. and M.S.E. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2008 and 2010, respectively. He is currently working toward the Ph.D. degree at the University of Michigan, Ann Arbor.

**Sunjay Dodani** received the B.S. degree in electrical engineering *(cum laude)* in 2007, the M.S. degree in biomedical engineering *(magna cum laude)* in 2008, and the Ph.D. degree in biomedical engineering in 2013, from the University of Michigan, Ann Arbor, MI, USA.

He has worked at Abbott Laboratories as an R&D engineer and corporate strategist in the United States and in Singapore supporting the Asia and Africa regions. He has also been a surgical research associate at the University of Michigan Hospital in the neuro-

surgery department. Dr. Dodani was apart of the healthcare IT company, Castlight Health prior to its IPO, leading strategic insight initiatives for the business. He is currently a product manager at Medallia, a private company focused in customer experience management.

Parag G. Patil studied electrical engineering at MIT (B.S. 1989) and philosophy and economics at Oxford University (M.A. 1991), before pursuing combined medical and doctoral studies in biomedical engineering at The Johns Hopkins University (MD-Ph.D. 1999). A childhood interest in brain-machine interfaces led to a strong clinical interest in Functional Neurosurgery, residency at Duke University (1999–2005) and fellowship training at the University of Toronto (2005–2006).

Dr. Patil is currently Assistant Professor of Neurosurgery, Neurology, Anesthesiology, and Biomedical Engineering at the University of Michigan. He is Co-Director of the Surgical Therapies Improving Movement (STIM) Program and Co-Director of the Psychiatric Neuromodulation Program. His clinical focus is neuromodulation and surgery for functional neurosurgical disorders including movement disorders, depression, epilepsy, and pain. His current research focuses on the mechanisms underlying the efficacy of DBS and other forms of neuromodulation as well as technological advances in DBS therapy.

Michael P. Flynn (SM'98) received the Ph.D. degree from Carnegie Mellon University, Pittsburgh, PA, USA, in 1995.

From 1988 to 1991, he was with the National Microelectronics Research Centre in Cork, Ireland. He was with National Semiconductor in Santa Clara, CA, USA, from 1993 to 1995. From 1995 to 1997, he was a Member of Technical Staff with Texas Instruments, Dallas, TX, USA. During the four-year period from 1997 to 2001, he was with Parthus Technologies, Cork, Ireland. He joined the University

of Michigan, Ann Arbor, MI, USA, in 2001, and is currently Professor. His technical interests are in RF circuits, data conversion, serial transceivers and biomedical systems.

Dr. Flynn is a 2008 Guggenheim Fellow. He received the 2011 Education Excellence Award and the 2010 College of Engineering Ted Kennedy Family Team Excellence Award from the College from Engineering at the University of Michigan. He received the 2005–2006 Outstanding Achievement Award from the Department of Electrical Engineering and Computer Science at the University of Michigan. He received the NSF Early Career Award in 2004. He received the 1992–1993 IEEE Solid-State Circuits Pre-doctoral Fellowship.

Dr. Flynn is Editor-in-Chief of the IEEE JOURNAL OF SOLID-STATE CIRCUITS, and a Distinguished Lecturer of the IEEE Solid-State Circuits Society. He has served as an Associate Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS and of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS. He serves on the Technical Program Committee of the European Solid-State Circuits Conference (ESSCIRC) and formerly served on the Technical Program Committees of the IEEE International Solid-State Circuits Conference (ISSCC), the Asian Solid-State Circuits Conference (A-SSCC), and the Symposium on VLSI Circuits.