# A Bidirectional Neural Interface Circuit With Active Stimulation Artifact Cancellation and Cross-Channel Common-Mode Noise Suppression

Adam E. Mendrela, *Student Member, IEEE*, Jihyun Cho, *Student Member, IEEE*, Jeffrey A. Fredenburg, *Member, IEEE*, Vivek Nagaraj, Theoden I. Netoff, Michael P. Flynn, *Fellow, IEEE*, and Euisik Yoon, *Member, IEEE*

Abstract—This work presents a bidirectional neural interface circuit that enables simultaneous recording and stimulation with a stimulation artifact cancellation circuit. The system employs a common average referencing (CAR) front-end circuit to suppress cross-channel environmental noise to further facilitate use in clinical environment. This paper also introduces a new range-adapting (RA) SAR ADC to lower the system power consumption. A prototype is fabricated in 0.18  $\mu m$  CMOS and characterized and tested in vivo in an epileptic rat model. The prototype attenuates stimulation artifacts by up to 42 dB and suppresses cross-channel noise by up to 39.8 dB. The measured power consumption per channel is 330 nW, while the area per channel is 0.17 mm².

*Index Terms*—Closed-loop stimulation, low power, neural recording, noise cancellation, SAR ADC.

#### I. INTRODUCTION

TUDIES have shown that neurostimulation, or direct current stimulation of neural tissue, significantly lessens symptoms in patients with neurological disorders. A 2-year study of a responsive neurostimulation system (NeuroPace) observed an average seizure reduction of 50% in 191 epilepsy patients [1]. Likewise, deep brain stimulation (DBS), a popular neurostimulation technique for treatment of various neurological diseases, has improved the quality of life for many patients worldwide [2]. Further adoption of neurostimulation as mainstream clinical treatment will be enabled in part by miniaturization of the electronics used to deliver stimulation current. A small form factor is important for implantable systems, while low power consumption is essential for long-term chronic deployment. Automated control of neurostimulation systems is also highly desired, as it would minimize patients' need for medical supervision and hospital visits. In an automated system, a closed-loop neural interface controls current stimulation to a particular brain region by monitoring the recorded neural signal from the neighboring neural tissue and adjusting

Manuscript received September 07, 2015; revised October 27, 2015; accepted November 25, 2015. This paper was approved by Guest Editor Masato Motomura.

A. E. Mendrela, J. Cho, J. A. Fredenburg, M. P. Flynn, and E. Yoon are with the Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109-2122 USA (e-mail: mendrela@umich.edu).

V. Nagaraj and T. I. Netoff are with the Department of Neuroscience, University of Minnesota, Minneapolis, MN 55455 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2015.2506651

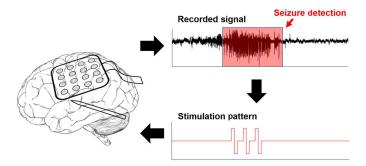

stimulation parameters in a feedback fashion. Fig. 1 demonstrates the general concepts where a closed-loop controller detects seizure-related biomarkers at the onset of a seizure and triggers a current pulse train to suppress the seizure. Such systems have been proven to successfully lower seizure occurrence rate [3], [4].

Recent research on neural interface systems has focused on reducing system power consumption and footprint area [5]–[7]. However, this research has rarely addressed problems related to the noisy environment and the side effects of stimulation. Proper operation of a closed-loop neural interface microsystem requires simultaneous recording and stimulation. In practice, continuous monitoring during stimulation presents a challenge due to large saturating artifacts appearing with the signal, as described in more detail in Section II. Only a few published techniques, such as signal blanking or symmetrical differential stimulation and recording, attempt to mitigate this problem [8], [9]. However, limitations in sensing capability and electrode design make these techniques unsuitable for universal use. In addition, recorded signals can be corrupted by common-mode environmental noise, which can come from motion artifacts or can be coupled from the power lines. This coupled noise significantly reduces the signal-to-noise ratio (SNR) in the recording channel.

To combat these problems, we present a novel neural interface system architecture incorporating new signal conditioning front-end features [10]. A mixed-signal adaptive stimulation artifact cancellation circuit removes stimulation artifacts at the front-end of the recording channels to prevent preamplifier saturation. A noise removal technique called common average referencing (CAR), implemented at the front-end, removes crosschannel common-mode noise and improves channel SNR. In addition, a new range-adapting (RA) SAR ADC architecture provides more power efficient digitization of the neural signal. These features, as well as other relevant system-level details, are presented in this paper in the following way. Section II discusses the cause of stimulation artifacts and explains the stimulation artifact cancellation algorithm. Section III analyzes the sources of common-mode noise and introduces the CAR algorithm. Section IV describes the circuit implementation of the new architectural elements as well as the new RA SAR ADC. Sections V and VI show recording channel characterization and in vivo measurements, respectively. Finally, conclusion is drawn in Section VII.

Fig. 1. Concept diagram of closed-loop stimulation for seizure suppression.

#### II. STIMULATION ARTIFACT CANCELLATION

#### A. Cause of Stimulation Artifacts

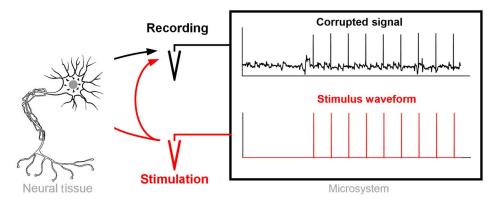

Stimulation artifacts inherently form at the recording interface during concurrent sensing and stimulation. Fig. 2 depicts simultaneous stimulation and recording and shows the corrupted recorded signal. We expect a stimulation-injected current to travel to a nearby neuron to affect its state by either triggering or inhibiting its spiking activity, while the recording probe monitors the neuron's activity throughout this process. Unfortunately, due to proximity of the recording and stimulation probes, a fraction of the stimulation current bypasses the neural tissue and directly couples onto the recording probe. Because the direct path is short and the stimulus current is usually larger than the neural extracellular ionic currents, the resulting stimulation artifact dominates the recorded signal. This leads to two problems. First, the large artifact current can saturate the sensitive preamplifier, causing signal loss and lowering the biomarker detection rate. An increased dynamic range (DR) might mitigate this problem but at the cost of high power consumption. Second, even if the artifacts do not saturate the amplifier, they might be mistaken for the biomarkers themselves, leading to a high false biomarker detection rate.

While there are many ways to alleviate the degraded performance, the most direct and best performing strategy is to cancel the artifacts as early as possible in the recording signal chain to prevent saturation and signal loss. Previous approaches to artifact cancellation include signal blanking and symmetric sensing. In signal blanking, the input to the recording amplifier is simply turned OFF during stimulation [8]. While this prevents the amplifier from saturating and temporarily losing its input voltage bias, any signal appearing during the off-period is lost. In symmetric sensing, the recording and stimulation electrodes are placed in a particular configuration to differentially cancel the artifact [9]. Here, the stimulation site is placed equidistantly between two differential recording sites so that the artifact equally couples onto each recording channel is rejected by the differential amplifier. While the neural signal is preserved in this scheme, it requires an inflexible electrode configuration that possibly hinders the effectiveness of the stimulation. Instead, our adaptive approach provides a universal architecture for artifact cancellation in a wide variety of applications that preserves the recorded neural signal while avoiding the shortcomings of previous works.

#### B. Adaptive Cancellation of Artifacts

Our approach to artifact cancellation circuit stems from the similarity in coupling between stimulating and recording probes of a closed-loop stimulation microsystem to the near-end crosstalk (NEXT) problem in wireline communication systems. In NEXT, a strong transmitter output couples to the input of the sensitive receiver amplifier and corrupts the received signal, increasing the system's bit-error rate [11], [12]. However, by utilizing the direct correlation between the transmitted signal and the observed artifact, a number of filtering techniques have been developed to cancel the artifacts. One such technique, called *adaptive noise cancellation*, learns the filtered crosstalk noise response of the channel and subtracts it from the recorded signal [13]. Due to its simplicity and general applicability, we apply a similar approach to cancel neural stimulation artifacts in an implantable neural interface [14].

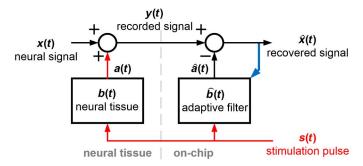

Analysis of the algorithm begins with the simplification of neural tissue response to a linear time-invariant (LTI) filter. The recorded signal y(t) can be expressed as a linear sum of the neural signal x(t) and the artifact a(t) as shown in Fig. 3. Furthermore, the artifact a(t) can be expressed as a stimulation signal s(t) filtered by the neural tissue response b(t)

$$y(t) = x(t) + a(t) = x(t) + b(t) *s(t).$$

(1)

Adaptive noise cancellation artificially recreates the response of the neural tissue in order to subtract it from the corrupted signal. To perform this task, an adaptive filter  $\hat{b}(t)$  (in Fig. 3) learns the impulse response of the neural tissue. When stimulation s(t) is fed through this filter, its output recreates the artifact  $\hat{a}(t)$  and this recreated artifact is subtracted from the recorded signal to cancel the real artifact as shown in the following equation:

$$\hat{x}(t) = ex(t) + a(t) - \hat{a}(t) = x(t) + b(t) *s(t) - \hat{b}(t) *s(t).$$

(2)

By inspection of the equation above, when the fully trained filter  $\hat{b}(t)$  approximates the neural response b(t), the stimulation term s(t) is cancelled, and the recovered output signal  $\hat{x}(t)$  approximately equals the original neural signal x(t).

A key block in adaptive noise cancellation is the learning algorithm of the adaptive filter. The least mean squares (LMS) learning algorithm, first presented by Widrow *et al.* and extensively used in telecommunications, is simple and reliable [15]. In LMS, the adaptive filter coefficients are updated every cycle to better approximate the desired response. The update quantity is derived by applying the steepest gradient descent approach to minimize power of the noise error  $\hat{x}(t)$ . As shown in [14], the online LMS algorithm predicts the coefficient update, needing only the value of the recovered output signal  $\hat{x}(t)$  from the previous cycle and the stimulation input s(t) as follows:

$$\hat{b}(t+1) = \hat{b}(t) + \mu s(t)\hat{x}(t). \tag{3}$$

<sup>1</sup>It is important to note that while the actual nonartifact neural response is also correlated to the stimulation signal, it is much delayed and not LTI; if the filter length is kept short enough, the real neural signal is not cancelled. The neural signal will thus be omitted in further explanation.

Fig. 2. Formation of stimulation artifacts and corruption of neural signal through direct coupling of stimulation signal to recording probe.

Fig. 3. System diagram of stimulation artifact addition and cancellation through adaptive filtering. The recorded signal  $y\left(t\right)$  is the corrupted neural signal picked up at the tissue–circuit interface, while the recovered signal  $\hat{x}\left(t\right)$  is the on-chip recovered neural signal.

The adaptation constant  $\mu$  is an adjustable knob for the user to trade adaptation speed for accuracy. A simplified version, called sign-sign LMS, eases the hardware requirements by performing computation on a sign-bit signal representation, resulting in the following update equation [16]:

$$\hat{b}(t+1) = \hat{b}(t) + \mu((s(t) \times \operatorname{sign}(\hat{x}(t))). \tag{4}$$

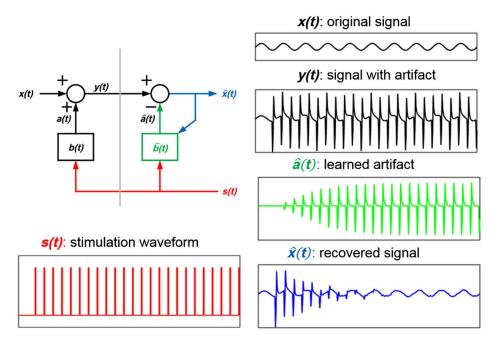

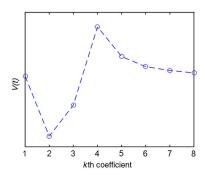

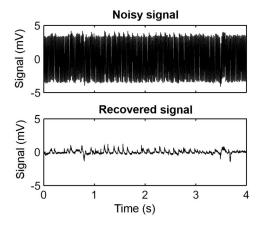

To show the effectiveness of the scheme, the algorithm is simulated with prerecorded neural data in Fig. 4. We artificially corrupt a known signal (here, a sinusoidal wave for clarity) with prerecorded artifact waveforms, added at predetermined times that are correlated to the stimulation waveform. As the algorithm runs for a few stimulation cycles, the filter output begins to resemble the added artifacts. In fact, the plotted impulse response of the adaptive filter at the end of simulation in Fig. 5 resembles a single added artifact, since the filtered artifact waveform is simply a pulse train convolved with a single eight sample long artifact-shaped sequence. Furthermore, the recovered signal shows a decrease in correlated crosstalk noise without significant distortion of the original uncorrelated signal.

The selection of the adaptive filter length was guided by maximizing the subtraction of artifact without removing the desired evoked neural potential. An analysis of typical electrocorticograph (ECoG) and local field potential (LFP) signals showed a 2 ms period between the stimulation pulse and earliest neural response, and during this time period, the artifact can be safely removed. Because the filter is sampled at the ADC frequency of 4 kHz, an 8 tap filter is sufficient to

attenuate most artifacts while preserving the nonartifact neural response.

#### III. COMMON-MODE NOISE REJECTION

As studied in [17], various environmental noise sources such as power lines and fluorescent lights capacitively couple onto the electrodes, the electrode wires, and the preamplifier inputs, potentially causing large amplitude common-mode noise. This noise can be cancelled through differential recording, where noise in two neighboring channels is rejected as common-mode signal. Inconveniently, differential recording requires the user to double the number of electrodes and may also remove important signals shared between the channels. As a compromise, a large single reference electrode is often used to subtract the reference noise from multiple channels without introducing localized neural signals. Unfortunately, because of the impedance mismatch between the recording and reference electrodes, line noise couples differently to the positive and negative inputs.

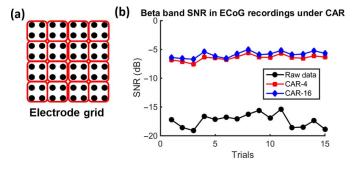

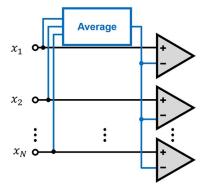

Instead of relying on a single electrode to provide an accurate reference signal, we can create a new reference signal from the existing channels. Ref. [18] creates this new reference signal in a software postprocessing scheme called CAR. CAR has become a common step in signal conditioning in neuroscientific literature [19], [20]. As shown in Fig. 6, the new reference signal is computed by averaging neighboring channels and subtracting this average from every channel. If used properly, the average holds most of the common-mode noise and little of neural signal, thus providing a clean, stable reference signal.

While it has been previously implemented as a software post-processing step, we implement CAR at the recording front-end. By cancelling the noise before final amplification and digitization, the DR constraints of the analog circuitry can be greatly relaxed. Challenges include unintended signal cancellation if the CM signal itself is of importance—this can be alleviated by averaging a sufficient number of channels so that the average contains a minimal amount of localized neural signal. Analysis of experimental neural data (in Fig. 7) shows that even a 4 channel CAR (CAR-4) can substantially improve SNR, while the use of 16 channel CAR (CAR-16) only slightly further increases SNR. This relatively small number of needed channels allows us to minimize the circuit area for CAR as described

Fig. 4. Simulation of the stimulation artifact cancellation algorithm with artificial neural data showing the system learning the response of the tissue.

Fig. 5. Final impulse response of the adaptive filter after training resembles the artifact waveform.

Fig. 7. (a) CAR-4 4 channel groupings mapped onto an ECoG electrode grid. (b) Comparison in SNR of ECoG recordings between raw data, active CAR-4, and active CAR-16 algorithms.

Fig. 6. Top-level diagram of CAR algorithm.

in Section IV-B. The common average reference can also be contaminated by a single very strong, or perhaps broken, channel. For this reason, the user should be able to eliminate that channel from the average calculation so that the noise does not bleed into other channels.

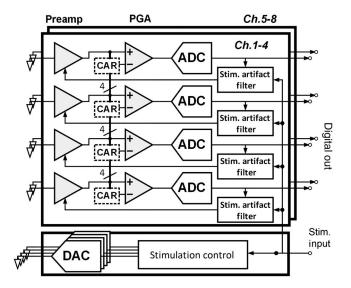

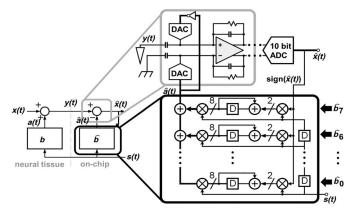

# IV. CIRCUIT IMPLEMENTATION

The proposed system architecture, shown in Fig. 8, consists of eight recording channels and four stimulation channels. Each recording channel consists of a preamplifier with a gain of 100, a programmable gain amplifier (PGA) with gain ranging from 1 to 10, and an ADC. The bandwidth of the preamplifiers is deliberately limited to a range of 1 Hz to 2 kHz to pass ECoG and LFP signals, which are most commonly used for neuromodulation control. The sampling rate of the ADC is set at 4 kS/s to properly sample the neural signals without aliasing. The resolution of the ADC is set to 10 bits to maintain the channel input-referred noise below 5  $\mu V_{\rm rms}$  (i.e., below the biological noise limit) while providing the ADC differential input DR of 1 V. The recording channels are split into two groups of four channels. In each group, every channel can be referenced to an average formed from any combination of these channels. The CAR circuit is placed after the preamplifier and before the PGA to remove the noise before final amplification and digitization. A stimulation artifact cancellation filter is implemented for every individual channel, as we cannot expect a similar coupled

Fig. 8. Top-level system architecture.

Fig. 9. Schematic of stimulation artifact cancellation circuit. Analog subtraction is framed in gray, while the adaptive filter is framed in black.

stimulation artifact for each channel. The stimulation data input is fed into the stimulation control block and also to the bank of stimulation artifact cancellation filters. Lastly, the stimulation channels themselves consist of current digital-to-analog converters (DACs) and digital timing and control circuitry. The current DAC resolution of 7 bits and DR up to 8 mA are enough for most neuromodulation applications.

#### A. Stimulation Artifact Cancellation Circuit

The stimulation artifact cancellation scheme is implemented with the mixed-signal circuit shown in Fig. 9. First, the single-bit stimulation input s(t) is fed through the digital adaptive filter. The filter output, or the digitally recreated artifact  $\hat{a}(t)$ , is converted into a differential analog signal using two DACs. This analog artifact replica is then subtracted from the corrupted neural signal at the preamplifier input to prevent signal saturation in the channel. Finally, the sign of digitized recovered signal  $\hat{x}(t)$  (from the 10 bit ADC) and single-bit stimulation signal s(t) are fed to the adaptive filter to train its coefficients.

A pair of capacitive DACs converts  $\hat{a}(t)$  into a differential analog signal. The DAC's 8 bit resolution is chosen to reduce

Fig. 10. Schematic of a single filter tap implementing LMS update and filter multiply and accumulate.

artifacts by up to 42 dB. From data analysis, this is sufficient to prevent channel saturation in most situations. While an increase in resolution would only result in a marginal increase in power consumption (less than 1 nW per channel for every additional bit), the area of the DAC would increase exponentially with extra resolution, since the LSB capacitor size is limited by mismatch. The 8 bit DAC resolution allows us to keep the area of the DAC below 12% of the complete channel layout area. A further advantage is that the capacitive DAC architecture offers the ability to scale the DAC LSB size, which corresponds to the  $\mu$  step size of the learning algorithm in (4), by adjusting the capacitive DAC reference voltage.

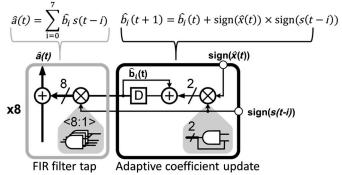

A standard 8 tap LMS digital adaptive filter nominally requires 16 multipliers and 15 adders to perform necessary computations, significantly contributing to the system power consumption and area. To minimize this overhead, we propose a simplified parallel architecture that eliminates computation elements by utilizing the sign–sign LMS algorithm in (4) that takes advantage of the simplified single-bit inputs.

First, the adaptive filter coefficients are updated by the following matrix combination:

$$\begin{bmatrix} \widehat{b_0}(t+1) \\ \widehat{b_1}(t+1) \\ \vdots \\ \widehat{b_7}(t+1) \end{bmatrix} = \begin{bmatrix} \widehat{b_0}(t) \\ \widehat{b_1}(t) \\ \vdots \\ \widehat{b_7}(t) \end{bmatrix} + \operatorname{sign}((\widehat{x}(t))) \begin{bmatrix} s(t) \\ s(t-1) \\ \vdots \\ s(t-7) \end{bmatrix}. \quad (5)$$

The sign of the error (or recovered) signal  $\hat{x}(t)$  is represented by the MSB of the recorded signal, and it is taken directly from the ADC output. The single-bit stimulation input, which represents a stimulation pulse with 1 and a lack of stimulation with 0, is fed from the stimulation circuit and is appropriately delayed by a shift register for each of the eight taps. The eight coefficient updates in (5) are then computed in parallel. Fig. 10 shows the hardware implementation of a single filter tap and coefficient update. On the right-hand side of Fig. 10, the single-bit s(t-i) input is multiplied by the sign of  $\hat{x}(t)$ . This multiplication, performed only with a single AND gate and a direct node connection, yields a 2 bit number representing -1, 0, or +1. This product is then added to the 8 bit  $\hat{b_i}(t)$  coefficient, computed and stored in the previous cycle, creating a new updated coefficient  $\hat{b_i}(t+1)$ .

Next, the  $\hat{b}\left(t\right)$  coefficients are fed to the FIR filter to compute the artifact replica using the following FIR filter matrix multiplication:

$$\widehat{a}(t) = \left[ \widehat{b_0}(t) \ \widehat{b_1}(t) \ \cdots \ \widehat{b_7}(t) \right] \begin{vmatrix} s(t) \\ s(t-1) \\ \vdots \\ s(t-7) \end{vmatrix}. \tag{6}$$

The computation above is implemented with eight multipliers and seven adders. Similar to the coefficient update described above, the multiplication and addition is performed in parallel for each tap, using a total of eight multipliers and seven adders. However, the single tap FIR filter multiplication is implemented with only eight AND gates, as shown in Fig. 10 on the left-hand side, since it uses a single-bit stimulation signal s (t-i) as the second operand. Finally, the seven 8 bit ripple-carry adders sum the multiplier outputs to create  $\hat{a}$  (t).

In summary, the full adaptive filter uses only 15 ripple-carry adders and no full multipliers. Because the filter runs at the very low ADC sampling frequency (4 kHz), the gates are minimum-sized to further reduce power consumption. Since most logic gates are active only when nonzero bits appear in the stimulation waveform, the average power consumption at conventional stimulation rates is below 11 nW and is almost negligible in comparison with the power consumption of the rest of the system.

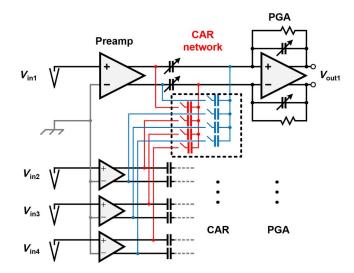

#### B. CAR Circuit

CAR is implemented at the input of the second-stage amplification to relax the DR of the PGA. The circuit implementation is shown in Fig. 11. Preamplifier outputs from four neighboring channels are fed into a capacitive averaging network, one per channel. An advantage of this approach is that it is passive and does not add to the total power consumption. Moreover, the switchable capacitor array allows full reconfigurability in case undesirable channels should be disconnected. The additional capacitors increase the area of the recording channel by less than 3% if the number of references is kept at 4 (sufficiency of this number of references is shown in Section III). Furthermore, these capacitors can be placed above the active circuitry to further save area. The averaged output is fed into the input of the PGA with opposing polarity alongside the original preamplifier connection to effectively subtract the CAR signal. To maintain the proper functioning of the averaging when changing the number of reference channels, input and feedback capacitors are connected or disconnected to maintain constant gain. Also, the output impedance of the preamplifiers must be low enough, so that the changing preamplifier output load due to switching capacitors does not significantly affect the bandwidth.

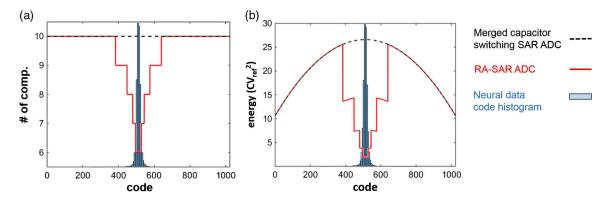

#### C. Range-Adapting SAR ADC

To further lower the average power consumption of recording channels, we also propose a new adaptive ranging technique for SAR ADCs. Typical recording channels must have a high

Fig. 11. CAR circuit implementation: the averaging CAR network is implemented for each channel in the group as shown for channel 1.

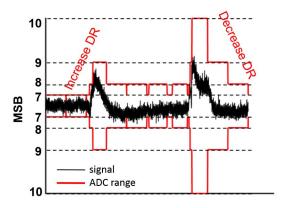

Fig. 12. Example of RA SAR ADC range (MSB) following the shape of a neural signal.

DR to process large signal amplitudes due to artifacts or periods of high neural activity. However, because high-amplitude activity in neural signals is relatively sparse, this high DR is often underutilized. By adapting the DR of the ADC to the signal, we can minimize the effective number of bits evaluated by the SAR algorithm and save power. Such system can be also applied to other types of sparse signals where the activity is low for majority of the time.

- 1) RA Algorithm: The RA algorithm adjusts the ADCs DR in two ways, as seen in Fig. 12. DR is automatically increased when a sample is detected to be out of range. DR can also be decreased between sampling cycles with an off-chip controller. Such a controller, e.g., can predict periods of low activity and reduce the range accordingly. In our simple implementation, a timer is set to decrease the DR by a single bit every 200 ms. Any algorithm which would adjust the range to fit the approximate envelope of the signal may be considered desirable; however, such algorithm should not alter the ADC's range at every sample since every range calculation requires extra logic power and it can dominate ADC power consumption.

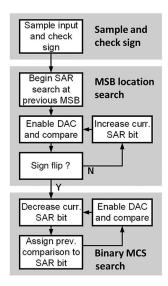

- 2) RA SAR Switching Scheme: The RA algorithm is easily implemented in an SAR ADC with a modified capacitor DAC

Fig. 13. RA SAR algorithm logic flowchart.

switching scheme by taking advantage of a specific applicationadapted binary search, similar to [21]. Our scheme is divided into three phases outlined in Fig. 13, namely: 1) sample and sign check phase; 2) MSB range search; and 3) binary LSB search. Fig. 14 shows two conversion examples for an in-range and out-of-range samples by tracking the comparator input voltage. First, stage (1) finds the sign of the sampled voltage. The sign determines which direction the capacitive DAC changes the comparator input voltage for each SAR bit. Only in stage (2), does the algorithm search for the location of MSB. The search algorithm makes its initial guess based on the previous sample MSB location which is stored in between samples (bit 7 for both cases in the example). The DAC assigns the previously found sign bit to the current MSB location, and the comparator checks if the polarity has changed. If it does not change, the algorithm performs additional trials by increasing the MSB location, switching in the appropriate capacitors in the DAC, and observing the comparator result. When the comparator output finally changes, or when the maximum MSB is reached, the algorithm keeps the found MSB and moves on to stage (3). At this time, operating in stage (3), the ADC performs the traditional binary search from the current MSB to determine the remaining bits. In our scheme, the merged capacitor switching (MCS) scheme is used to minimize capacitor switching and power consumption [22].

The proposed RA SAR switching scheme has two key advantages. First, the range-checking phase prevents the ADC from losing any sample information, as the capacitor switching is performed without losing any charge on the top plate. Second, if the range-checking phase accepts the initial MSB location guess and does not have to perform additional trials, the ADC does not have to switch its comparator and DAC capacitors for all the bits in the ADC. This, on average, greatly reduces the power consumption of the ADC comparator and the capacitor DAC. As previously mentioned, [21] also presents an RA SAR ADC algorithm which, in contrast, begins the search at previous sample's LSB. Our proposed RA SAR algorithm is better suited

Fig. 14. Comparator input voltage during RA SAR A-to-D conversions for inrange and out-of-range samples, respectively. The conversion phases and bit cycles (bit) are also shown.

for signals which exhibit low amplitudes but are not smooth and maintain high variance relative to maximum amplitude, as it is often the case in neural recordings.

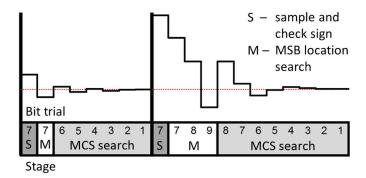

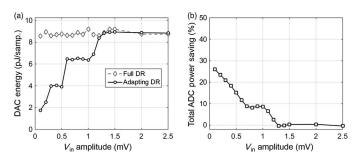

3) ADC Power Consumption: Fig. 15 demonstrates the possible power reduction in an RA SAR ADC. Fig. 15(a) plots the minimum number of comparisons in the case of correct initial range guess for every code in the 10 bit ADC. Note that the minimum initial guess is kept at the sixth bit because neural signals rarely maintain lower amplitudes. The biggest power reduction when compared to a traditional MSC SAR ADC scheme is observed for small input signals. This is due to the reduced number of significant bits checked by the RA algorithm.

A code histogram of previously recorded neural data is overlaid to show that a great majority of the signal does fall in the power-saving range. In fact, simulations showed a 25% reduction in the average number of comparisons. In Fig. 15(b), the capacitive DAC switching energy per code is plotted for the MCS and RA switching schemes. Similar to the previous analysis, the greatest power savings are found in the middle codes. A 72% reduction in average DAC power consumption is observed.

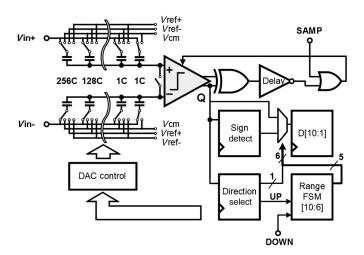

4) ADC Circuit Implementation: The SAR ADC is implemented in differential fashion and employs bottom-plate input sampling to reduce parasitic error (Fig. 16). The ADC also uses an asynchronous architecture. At the beginning of every sample, the sampling clock triggers a self-timing delay loop that first clocks the comparator. When the comparator makes the decision, it activates the SAR logic and sends a signal through an inverter-based delay line to give time for settling of the capacitive DAC and to retrigger the comparator for the next bit conversion cycle.

The SAR logic executes the RA algorithm. The stages of the algorithm are controlled by the "direction select" flip-flop and logic. In stage (1), the comparator output Q is stored onto the "sign detect" flip-flop. After that, the "direction select" state tells the SAR logic to assign the sign bit to the current MSB location stored in a finite-state machine (range FSM). The range FSM is a 5 bit one-hot counter that saves the MSB location in between ADC samples and it increases or decreases its value as required by the RA algorithm. A mux, controlled by the range FSM and the "direction select" flip-flop, selects the

Fig. 15. (a) Simulated minimum number of comparisons and (b) capacitive DAC switching energy for 10 bit RA SAR ADC as compared to a MCS SAR ADC. Overlaid neural data code histogram shows most data falls within the most efficient code range.

Fig. 16. RA SAR ADC architecture schematic.

SAR flip-flops that will be assigned the sign bit. As the logic detects the comparator polarity change at the end of stage (2), the "direction select" flip-flop changes its state and begins the MCS search of stage (3), finds the remaining bits, and stores them into the 10 bit SAR flip-flops. In between the samples, the range FSM can be externally triggered by the DOWN control input to decrease the initial MSB location to be used in the next sample conversion.

## V. MEASUREMENTS

# A. System Performance

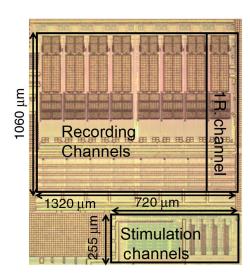

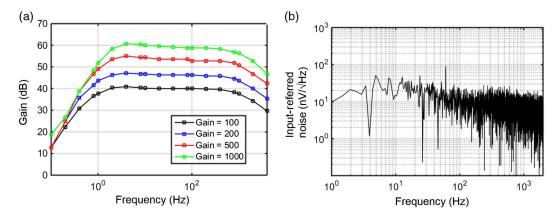

The prototype is fabricated in 0.18  $\mu m$  CMOS. Fig. 17 shows the chip microphotograph. The total area of the recording circuit is  $1.4~mm^2$  or  $0.17~mm^2$  per channel, while the area of the stimulation circuit is  $0.18~mm^2$ . Fig. 18(a) shows the measured frequency response of the recording channel for four gain settings: 100, 200, 500, and 1000. Each of the gain settings maintains a bandwidth of 1 Hz to 2 kHz. Fig. 18(b) shows the input-referred noise of the full recording channel at the ADC output with a shorted input. The total measured input-referred noise is  $3.05~\mu V_{\rm rms}$  between 1 Hz and 2 kHz. The measured power consumption per recording channel is  $0.33~\mu W$ .

Fig. 17. Chip microphotograph.

### B. CAR Circuit Measurements

An *in vitro* experiment with a 4 channel recording was conducted to test the functionality of the CAR circuit. The 4 channel waveforms were constructed from a synchronized 60 Hz noise signal. A prerecorded neural signal was then added to one of the channels. The top plot in Fig. 19 shows the channel with merged 60 Hz noise and the prerecorded signal. When CAR is switched ON for the 4 channel group, as shown in the bottom of Fig. 19, the averaged reference reduces the recorded 60 Hz power by -36 dB, effectively increasing the recording channel SNR by the same amount.

## C. ADC Measurements

The average power consumption of the ADC is 89 nW when measured at 4 kS/s for a full-range sinusoid input. To test the functionality of the RA algorithm, the channel input signal amplitude is swept while monitoring the power consumption of the full ADC and DAC. Fig. 20 shows a significantly reduced DAC energy consumption for low-amplitude inputs (by more than a factor of 4). The shape of the plot is similar to the predicted DAC energy consumption from Fig. 15. This amounts

Fig. 18. (a) Recording channel frequency response for four gain settings measured at ADC output. (b) Input-referred noise of the full recording channel.

Fig. 19. Full channel recording before and after activating the CAR-4 circuit, showing the common-mode (60 Hz) noise reduction in *in vitro* recording.

Fig. 20. ADC measurements showing (a) capacitive DAC energy consumption per sample for enabled/disabled adapting DR algorithm for amplitude-swept sinusoid input and (b) ADC total power savings.

to total ADC power consumption saving of more than 25% for low-amplitude inputs.

#### VI. IN VIVO MEASUREMENTS

A series of *in vivo* tests were performed to test the system functionality in a real application. Recordings were taken during the stimulation of a rat hippocampus as the rat was under chemically induced seizures.<sup>2</sup> Seizures were induced

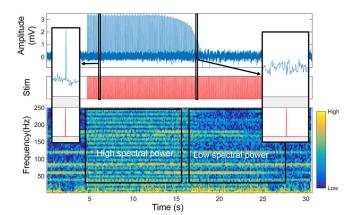

Fig. 21. In vivo experimental results showing stimulation artifact cancellation learning process for 12 Hz 600  $\mu$ A biphasic stimulation. Top plot shows the raw time-domain plot of the recording output, middle plot shows the stimulation timing, and the bottom plot shows the recorded output spectrogram.

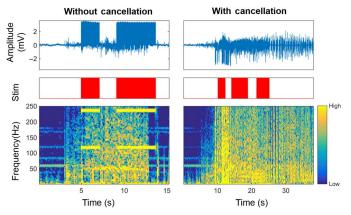

Fig. 22. Neural recordings of 120 Hz  $600\,\mu\text{A}$  biphasic stimulation during seizure activity (a) without activate artifact cancellation and (b) with active artifact cancellation.

following the injection of 4 aminopyradine unilaterally into the CA3 region of the hippocampus. The stimulation was then applied to the ventral hippocampal commissure (VHC) which bilaterally innervates the CA3 regions where the seizures are induced. A recording electrode was placed in the CA1 region of the hippocampus, close to the injection region. In this setup,

<sup>&</sup>lt;sup>2</sup>The *in vivo* experiments were performed at the Netoff Epilepsy and Neuroengineering Laboratory, University of Minnesota under the approval from the Institutional Animal Care and Use Committee.

|                                             | [21]    | [22]    | [23]   | This work |

|---------------------------------------------|---------|---------|--------|-----------|

| Technology                                  | 0.18 μm | 0.13 μm | 65 nm  | 0.18 μm   |

| Area (per recording ch.) (mm <sup>2</sup> ) | ~0.42   | ~0.625  | 0.025  | 0.17      |

| Rec. power (µW/ch.)                         | 7.35    | 4.2     | 2.3    | 0.33      |

| BW (Hz)                                     | ~0.5–7k | 0-320   | 1-0.5k | 1-2k      |

| IR noise (μV <sub>rms</sub> )               | 5.23    | 2       | 1.32   | 3.05      |

| Stimulation artifact cancellation           | No      | No      | No     | Yes       |

| CAR                                         | No      | No      | No     | Yes       |

TABLE I

PERFORMANCE SUMMARY AND COMPARISON WITH OTHER RECENT WORKS

the recording electrode has a clear recording of the seizure activity and the proximity of the recording and stimulation electrodes results in large stimulation artifacts that test the artifact removal algorithm.

In initial experiments, recordings were taken when stimulating the tissue as the artifact cancelling algorithm trained the filter weights. In Fig. 21, a 12 Hz 600 µA biphasic pulse stimulation train is applied and the response is recorded in time and time-frequency domain. As the stimulation begins in the fifth second, large artifacts clearly dominate the recorded waveform. Because the artifacts are being clipped at the start of stimulation, the reduction in artifacts is not apparent until the 15th second as the filter weights become large enough to successfully reduce the recorded artifacts. When the filter weights approach their steady-state values, the artifacts are reduced to the below-noise level. In a latter experiment, shown in Fig. 22, we stimulated the brain with and without cancellation as the seizures were episodically occurring. The noncancelled artifacts from the 120 Hz stimulation clearly dominate the seizure activity both in time and frequency domain. After the cancellation filter is turned ON, the artifacts disappear below the visible seizure signal, clearly showing the improved signal quality as the seizure signal becomes unobstructed by the artifact peaks. Across trials, artifacts are suppressed on average by at least 24 dB; however, this number could be even higher if not for the high biological noise masking the suppressed artifacts. Note that the full learning process needs to be performed only once after implantation, as the neural tissue response does not change significantly during chronic use of stimulation.<sup>3</sup>

#### VII. CONCLUSION

We present a new bidirectional neural interface circuit for closed-loop stimulation. The microsystem introduces novel architectural features to combat environmental noise such as stimulation artifacts and cross-channel common-mode noise, allowing overall proper closed-loop control. The circuit also includes a new RA SAR ADC to reduce power consumption. The system was fully characterized and verified *in vivo*. Table I summarizes and compares few key specifications with previously published works highlighting the state-of-the-art performance. Our work maintains a relatively low area and low noise in comparison with the published ECoG recording ICs in [23]–[25]. However, at lower power consumption, the system

<sup>3</sup>When the filter coefficients reach a steady state, the adapting algorithm can be turned OFF to maintain their constant value. It can also be periodically turned ON to adapt coefficients to a slowly changing neural tissue response.

implements new functionality which enables the use in a wider variety of applications.

#### REFERENCES

- [1] C. N. Heck *et al.*, "Two-year seizure reduction in adults with medically intractable partial onset epilepsy treated with responsive neurostimulation: Final results of the RNS system pivotal trial," *Epilepsia*, vol. 55, no. 3, pp. 432–441, 2014.

- [2] M. L. Kringelbach, N. Jenkinson, S. L. F. Owen, and T. Z. Aziz, "Translational principles of deep brain stimulation," *Nat. Rev. Neurosci.*, vol. 8, no. 8, pp. 623–635, 2007.

- [3] A. Berényi, M. Belluscio, D. Mao, and G. Buzsáki, "Closed-loop control of epilepsy by transcranial electrical stimulation," *Science*, vol. 337, no. 6095, pp. 735–737, Aug. 2012.

- [4] F. T. Sun, M. J. Morrell, and R. E. Wharen, "Responsive cortical stimulation for the treatment of epilepsy," *Neurotherapeutics*, vol. 5, no. 1, pp. 68–74, Jan. 2008.

- [5] A. Borna and K. Najafi, "A low power light weight wireless multichannel microsystem for reliable neural recording," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 439–451, Feb. 2014.

- [6] H. Rhew, J. Jeong, J. Fredenburg, and S. Dodani, "A fully self-contained logarithmic closed-loop deep brain stimulation SoC with wireless telemetry and wireless power management," *IEEE J. Solid-State Circuits*, vol. 49, no. 10, pp. 2213–2227, Oct. 2014.

- [7] R. Muller, S. Member, S. Gambini, and J. M. Rabaey, "A 0.013 mm<sup>2</sup>, 5 μW, DC-coupled neural signal acquisition IC with 0.5 V supply," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 232–243, Jan. 2012.

- [8] S. Archer and B. Pless, "Stimulation signal generator for an implantable device," U.S. Patent 6 690 974 B22004, Feb 10, 2004.

- [9] S. Stanslaski *et al.*, "Design and validation of a fully implantable, chronic, closed-loop neuromodulation device with concurrent sensing and stimulation," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 20, no. 4, pp. 410–421, Jul. 2012.

- [10] A. E. Mendrela, J. Cho, J. A. Fredenburg, C. A. Chestek, and M. P. Flynn, "Enabling closed-loop neural interface: A bi-directional interface circuit with stimulation artifact cancellation and cross-channel CM noise suppression," in *Proc. Symp. VLSI Circuits*, 2015, pp. 108–109.

- [11] Y. Hur et al., "Equalization and near-end crosstalk (NEXT) noise cancellation for 20-Gb/s 4-PAM backplane serial I/O interconnections," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 1, pp. 246–254, Jan. 2005.

- [12] C. Pelard, E. Gebara, and A. Kim, "Realization of multigigabit channel equalization and crosstalk cancellation integrated circuits," *IEEE J. Solid-State Circuits*, vol. 39, no. 10, pp. 1659–1670, Oct. 2004.

- [13] B. Widrow, J. R. Glover, and J. M. McCool, "Adaptive noise cancelling: Principles and applications," *Proc. IEEE*, vol. 63, no. 12, pp. 1692–1716, Dec. 1975.

- [14] J. W. Gnadt, S. D. Echols, A. Yildirim, H. Zhang, and K. Paul, "Spectral cancellation of microstimulation artifact for simultaneous neural recording in situ," *IEEE Trans. Biomed. Eng.*, vol. 50, no. 10, pp. 1129–1135, Oct. 2003.

- [15] B. Widrow and J. McCool, "Stationary and nonstationary learning characteristics of the LMS adaptive filter," *Proc. IEEE*, vol. 64, no. 8, pp. 1151–1162, Aug. 1976.

- [16] S. Dasgupta and C. R. Johnson, "Some comments on the behavior of sign-sign adaptive identifiers," Syst. Control Lett., vol. 7, no. 2, pp. 75–82, 1986.

- [17] C. K. Thorp and P. N. Steinmetz, "Interference and noise in human intracranial microwire recordings," *IEEE Trans. Biomed. Eng.*, vol. 56, no. 1, pp. 30–36, Jan. 2009.

- [18] K. A. Ludwig, R. M. Miriani, N. B. Langhals, M. D. Joseph, D. J. Anderson, and D. R. Kipke, "Using a common average reference

- to improve cortical neuron recordings from microelectrode arrays," *J. Neurophysiol.*, vol. 101, no. 3, pp. 1679–1689, 2009.

- [19] K. J. Miller, S. Zanos, E. E. Fetz, M. den Nijs, and J. G. Ojemann, "Decoupling the cortical power spectrum reveals real-time representation of individual finger movements in humans," *J. Neurosci.*, vol. 29, no. 10, pp. 3132–3137, Mar. 2009.

- [20] C. A. Chestek et al., "Hand posture classification using electrocorticography signals in the gamma band over human sensorimotor brain areas," J. Neural Eng., vol. 10, no. 2, pp. 1–11, Apr. 2013.

- [21] F. M. Yaul and A. P. Chandrakasan, "A 10 b 0.6 nW SAR ADC with data-dependent energy savings using LSB-first successive approximation," IEEE J. Solid-State Circuits, vol. 57, no. 12, pp. 198–199, 2014.

- [22] V. Hariprasath, J. Guerber, S.-H. Lee, and U.-K. Moon, "Merged capacitor switching based SAR ADC with highest switching energy-efficiency," *Electron. Lett.*, vol. 46, no. 9, p. 620, 2010.

- [23] W. M. Chen et al., "A fully integrated 8-channel closed-loop neural-prosthetic CMOS SoC for real-time epileptic seizure control," IEEE J. Solid-State Circuits, vol. 49, no. 1, pp. 232–247, Jan. 2014.

- [24] Y. Zhang *et al.*, "A batteryless 19 µW MICS/ISM-band energy harvesting body sensor node SoC for ExG applications," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 199–213, Jan. 2013.

- [25] R. Muller et al., "A minimally invasive 64-channel wireless μECoG implant," IEEE J. Solid-State Circuits, vol. 50, no. 1, pp. 344–359, Jan. 2015

Adam E. Mendrela (S'11) received the B.S. degree in electrical and computer engineering from Cornell University, Ithaca, NY, USA, in 2012, and the M.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2014, where he is currently pursuing the Ph.D. degree in electrical engineering.

His research interests include developing new IC architectures for neural interfacing systems, mixed-signal electronics, signal processing, and neural engineering.

**Jihyun Cho** (S'11) received the B.S. and M.S. degrees in electrical engineering from Yonsei University, Seoul, South Korea, in 2005 and 2007, respectively. He is currently pursuing the Ph.D. degree in electrical engineering at the University of Michigan, Ann Arbor, MI, USA.

From 2007 to 2010, he was a Lecturer with ROK Air Force Academy, Cheongwon, South Korea. His research interests include CMOS image sensor and mixed-signal VLSI circuit design.

**Jeffrey A. Fredenburg** (S'08–M'15) received the Ph.D. degree in Electrical Engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015.

He joined Movellus Circuits, Ann Arbor, MI, USA.

Vivek Nagaraj received the M.S. degree in cognitive neuroscience and B.S. degree in biology from the University of Texas at Dallas, Richardson, TX, USA, in 2007 and 2011, respectively. He is currently pursuing the Ph.D. degree in neuroscience at the University of Minnesota, Minneapolis, MN, USA.

He is currently a Research Assistant with the Netoff Lab, Biomedical Engineering, University of Minnesota. His research interests include developing closed-loop patient specific neuromodulation therapies for epilepsy.

**Theoden I. Netoff** received the Ph.D. degree in neuroscience from George Washington University, Washington, DC, USA, in 2001.

He is currently an Associate Professor of Biomedical Engineering with the University of Minnesota, Minneapolis, MN, USA. His research interests include developing new and optimizing current therapeutic approaches for treatment of Parkinson's disease and epilepsy.

Michael P. Flynn (F'15) received the B.E. and M.Eng.Sc. degrees from the University College Cork, Cork, Ireland, in 1988 and 1990, respectively, and the Ph.D. degree from Carnegie Mellon University, Pittsburgh, PA, USA, in 1995, all in Electrical Engineering.

From 1988 to 1991, he was with the National Microelectronics Research Centre, Cork, Ireland. From 1993 to 1995, he was with the National Semiconductor, Santa Clara, CA, USA. From 1995 to 1997, he was a Member of Technical Staff with

Texas Instruments, Dallas, TX, USA. From 1997 to 2001, he was with Parthus Technologies, Cork, Ireland. He joined the University of Michigan, Ann Arbor, MI, USA, in 2001, and is currently a Professor. His research interests include data conversion, RF circuits, serial transceivers, and biomedical systems.

Dr. Flynn is a 2008 Guggenheim Fellow. He received the 1992-1993 IEEE Solid-State Circuits Predoctoral Fellowship. He was an Associate Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC) and an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II. He has served on the Technical Program Committees of the International Solid-State Circuits Conference (ISSCC), the Symposium on VLSI Circuits, and the Asian Solid-State Circuits Conference (ASSCC). He was a Distinguished Lecturer of the IEEE Solid-State Circuits Society. He currently serves on the Technical Program Committee of the European Solid-State Circuits Conference (ESSCIRC). He is the Editor-in-Chief of the IEEE JOURNAL OF SOLID-STATE CIRCUITS. He was the recipient of the 2011 Education Excellence Award and the 2010 College of Engineering Ted Kennedy Family Team Excellence Award from the College of Engineering, University of Michigan. He was also the recipient of the 2005-2006 Outstanding Achievement Award from the Department of Electrical Engineering and Computer Science, University of Michigan; and the NSF Early Career Award in 2004.

Euisik Yoon received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, South Korea, in 1982 and 1984, respectively, and the Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 1990.

From 1990 to 1994, he worked with the National Semiconductor Corp., Santa Clara, CA, USA, where he engaged in researching deep submicron CMOS integration and advanced gate dielectrics. From 1994 to 1996, he was a Member of Technical Staff with

the Silicon Graphics Inc., Mountain View, CA, USA, where he worked on the design of the MIPS microprocessor R4300i and the RCP 3-D graphic coprocessor. He took faculty positions with the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejon, South Korea (1996–2005), and with the Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN, USA (2005–2008), respectively. During the academic year of 2000–2001, he was a Visiting Faculty at Agilent Laboratory, Palo Alto, CA, USA. In 2008, he joined the Department of Electrical Engineering and Computer Science, University of Michigan, where he is currently a Professor and the Director of Lurie Nanofabrication Facility and the Director of NSF International Program for the Advancement of Neurotechnology (IPAN). His research interests include MEMS, integrated microsystems, and VLSI circuit design.

Dr. Yoon has served on various Technical Program Committees including the Microprocesses and Nanotechnology Conference (1998), the International Sensor Conference (2001), the IEEE Asia-Pacific Conference on Advanced System Integrated Circuits (2001–2002), the International Conference on Solid-State Sensors, Actuators, and Microsystems (Transducers) (2003 and 2005), the IEEE International Electron Device Meeting (2006–2008), and the IEEE International Conference on Micro Electro Mechanical Systems (2006, 2009–2010). He also served on the IEEE International Solid-State Circuit Conference Program Committee (2003–2007) and was a General Chair of the International Symposium on Bio Micro and Nanosystems (2005).