# A 16-Element 4-Beam 1 GHz IF 100 MHz Bandwidth Interleaved Bit Stream Digital Beamformer in 40 nm CMOS

Sunmin Jang<sup>®</sup>, Student Member, IEEE, Jaehun Jeong, Member, IEEE, Rundao Lu, Student Member, IEEE, and Michael P. Flynn, Fellow, IEEE

Abstract—A 1 GHz intermediate frequency, 16-element, 4-beam digital beamformer facilitates multi-in multi-out, 5G mobile, and other emerging communication standards. Digital beamforming has been limited by high power consumption, large die area, and the need for a large number of analogto-digital converters (ADCs). The proposed digital beamformer addresses these issues by combining interleaved bit stream processing (IL-BSP) with power- and area-efficient continuoustime bandpass delta-sigma modulators (CTBPDSMs). Compared to conventional DSP, IL-BSP reduces both power and area by 80%. The new CTBPDSM architecture reduces ADC area by 67% and the energy per conversion by 43% with a powerand area-efficient three-stage nested  $G_m$ -C op-amp and a passive summer. With an 11.2 dB array gain, the digital beamformer achieves a 58.5 dB signal to noise and distortion ratio and a 59.6 dB SNR over a 100 MHz bandwidth. Thanks to the accurate digitization and digital processing, the measured beam patterns of the four simultaneous beams are near ideal.

Index Terms—5G mobile communication, bit stream processing (BSP), delta-sigma modulation, digital beamforming (DBF), linear antenna array, linearity, multi-in multi-out (MIMO), phased array, receiver.

## I. INTRODUCTION

**5** G wireless systems will use millimeter-wave bands to support more users and deliver higher data rates [1]. However, millimeter-wave systems face severe link-budget challenges due to high path losses and the lower diffraction of millimeter-wave signals [2], [3]. Large array beamforming is an essential technology to make up for the reduced link budgets with array gain and to establish a reliable wireless connection through multi-in multi-out (MIMO) algorithms.

Digital beamforming (DBF) has several advantages over analog beamforming (ABF) including accurate beam patterns, multiple receive beams without SNR penalty, adaptive interference suppression, simplified calibration, and fully reconfigurable beam shape flexibility [4]. Seamless generation of multiple simultaneous beams in DBF allows us to exploit MIMO techniques for improved reliability and higher data rates. For example, transmit diversity improves resistance

Manuscript received August 30, 2017; revised November 14, 2017; accepted December 25, 2017. This paper was approved by Associate Editor Osama Shanaa. This work was supported by DARPA ACT. (Corresponding author: Sunmin Jang.)

S. Jang, R. Lu, and M. P. Flynn are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: smjang@umich.edu).

J. Jeong is with Broadcom, Irvine, CA 92617 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2018.2791483

to multipath fading by receiving a single data stream via multiple beams [5]. Spatial multiplexing, in which different data streams are received through different beams, can also achieve higher data rates or further reduce the SNR requirement of the receiver [6]. However, DBF is limited in practice by high power consumption and large die area [7].

To reduce the power dissipation, [8] presents a digital beamformer implemented with a bit stream processing (BSP) approach. This BSP beamformer prototype achieves 64% lower power and 68% smaller area compared to a conventional DSP-based beamformer. BSP saves power and area by implementing complex digital multiplication with simple multiplexers (MUX) and reducing the number of decimators from the number of channels to the number of beams. However, the digital beamformer prototype in [8] is limited to 20 MHz bandwidth, eight elements, and two simultaneous beams.

Paving the way for large scale MIMO for 5G communication, we present a digital, 16-element, 4-beam beamformer with a 100 MHz bandwidth. A 4 GS/s analog-to-digital converter (ADC) with an oversampling ratio (OSR) of 20 supports a 100 MHz bandwidth. A challenge is that the approach in [8] necessitates that the digital circuitry also runs at 4 GHz, which is difficult in 40 nm CMOS. Furthermore, it is critical to have power- and area-efficient ADCs, as 16 are needed. To overcome these challenges, we introduce interleaved BSP (IL-BSP), which reduces both power and area by 80% compared to a DSP implementation. We also utilize compact and efficient continuous-time bandpass delta-sigma modulators (CTPBDSMs), which occupy only 1/3 of area and consume 43% less energy per conversion than the ADCs in [8].

This paper is an extension of [9] and is organized as follows. Section II compares the ADC power consumption for DBF and ABF. Section III details the implementation of the IL-BSP. Section IV presents the circuit implementation of the CTBPDSM, and Section V introduces the system architecture of the IL-BSP digital beamformer. Section VI provides measured results of the prototype beamformer IC, and Section VII concludes this paper.

## II. ADC POWER COMPARISON FOR DIGITAL AND ANALOG BEAMFORMING

Although DBF requires a large number of ADCs, if the ADCs are noise limited then the total ADC power for DBF and ABF is comparable.

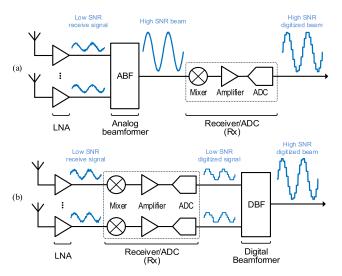

Fig. 1. System architectures of (a) analog and (b) digital beamforming.

#### A. Thermal Noise Limited

Although DBF requires a large number of ADCs, the array gain in DBF greatly relaxes the ADC SNR requirement. Furthermore, if we assume that the ADCs are noise limited, then the total ADC power is the same for both cases.

ABF necessitates a high ADC SNR to quantize the high SNR beam since beamforming is performed prior to the ADC [Fig. 1(a)]. Although DBF necessitates several ADCs, the SNR requirement of a single ADC can be greatly relaxed, as the lower SNR signals from the individual ADCs combine to generate a high SNR beam [Fig. 1(b)]. The SNR requirement of the ADCs in ABF and in N-element DBF is expressed

$$SNR_{ABF} = SNR_{target}$$

(1)

$$SNR_{DBF} = \frac{SNR_{target}}{N}$$

(2)

where SNR<sub>target</sub> is the SNR requirement of the system, SNR<sub>ABF</sub> is the SNR requirement of the single ADC in ABF, and SNR<sub>DBF</sub> is the SNR requirement of one of the ADCs in DBF. As shown in (1) and (2), SNR<sub>DBF</sub> is N times lower than SNR<sub>ABE</sub>, as N-element DBF exploits a digital array gain of N. (Receive signals from channels constructively interfere to generate  $N^2$  times higher signal power, and uncorrelated noise from channels produce N times greater noise power.)

With an assumption that the ADCs in DBF and ABF have the same Schreier figure of merit (FoM), the total power consumption of the ADCs in ABF and DBF can be represented as

$$P_{\text{ABF}} = \frac{\text{SNR}_{\text{ABF}} * \text{BW}}{\text{FoM}_{\circ}} \tag{3}$$

$$P_{ABF} = \frac{SNR_{ABF} * BW}{FoM_s}$$

$$P_{DBF} = \frac{SNR_{DBF} * BW}{FoM_s} * N$$

(4)

where  $P_{ABF}$  is the power consumption of the ADC in ABF and  $P_{\text{DBF}}$  is the power consumption of all ADCs in DBF. As  $SNR_{DBF}$  is N times lower than  $SNR_{ABF}$ , the total power consumption of all the ADCs in DBF is the same as the single ADC power consumption in ABF when the ADCs are limited by noise.

Fig. 2. Digital beamformers in (a) DSP and (b) BSP implementations.

## B. Interference Limited

When a beamformer receives M interference signals, the total received input power of an ADC can be represented as  $(\sum_{m=1}^{M} I_m) + S$ , where  $I_m$  is the *m*th interference power and S is the signal power. In this case, the SNR requirement of the ADC becomes  $10 \log_{10} ((\sum_{m=1}^{M} (I_m/S)) + 1)$  dB higher. For example, when we have one interferer that sends the exact the same power as the signal transmitter at the same distance, the SNR requirement of the ADC in a digital beamformer increase by 3.01 dB (0.5 bit effective number of bits). The SNR requirement for an analog beamformer does not increase by as much because the interference is attenuated. If the mth interference is attenuated by  $N_m$  dB, the SNR requirement of an ADC in an analog beamformer increases by  $10 \log_{10}((\sum_{m=1}^{M} (I_m/s) 10^{-(N_m/10)}) + 1 \text{ dB}$ , which is lower than for DBF.

## III. DIGITAL BEAMFORMING ARCHITECTURE

## A. Bit Stream Processing Digital Beamformer

To understand bit stream beamforming, we first consider more conventional digital beamformer architecture with conventional DSP and low-pass delta-sigma modulators as shown in Fig. 2(a). Analog mixers downmix the receive signals and then low-pass delta-sigma modulators convert the downmixed signals to bit streams. Decimators convert the bit streams to low-sample-rate high-resolution digital signals. Phase shifting through digital multiplication and finally, addition of the phase-shifted signals generates a beam.

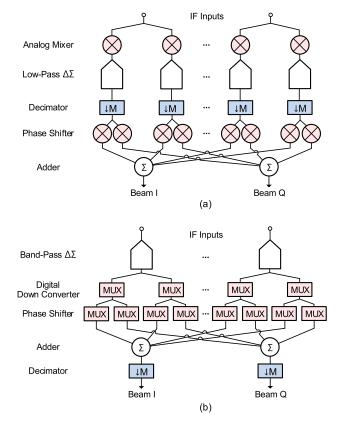

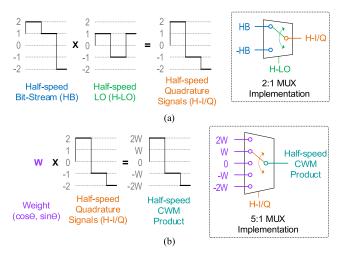

Fig. 3. MUX-based (a) digital downconversion and (b) CWM implementation in BSP.

In contrast, BSP implements high-speed digital multiplication with simple MUX operating directly on the lowresolution bit streams from bandpass ADCs [Fig. 2(b)], removing the need for a power and area hungry decimator in each channel [8]. A BSP digital downconverter (DDC) directly downconverts the bit stream from intermediate frequency (IF) to base band, by multiplying the bit stream with a digital local oscillator (LO) signal. The low-resolution quantizer in the CTBPDSM generates the five-level (-2, -1, 0, 1, 2)bit stream. A sampling frequency 4 times higher than the LO frequency results in a sampled LO signal represented as three levels (-1, 0, 1), as shown in Fig. 3(a). In [8], this multiplication operation is implemented with a 3:1 MUX using the three-level LO as the MUX select. The product of the multiplication between the three-level LO and the five-level bit stream remains a five-level signal.

Complex weight multiplication (CWM) can be expressed in a matrix form as

$$\begin{bmatrix} I'_k \\ Q'_k \end{bmatrix} = \begin{bmatrix} \cos(k\theta) & \sin(k\theta) \\ -\sin(k\theta) & \cos(k\theta) \end{bmatrix} \begin{bmatrix} I_k \\ Q_k \end{bmatrix}$$

(5)

$$\theta = 2\pi f_c \frac{\mathrm{dsin}\psi}{c}$$

(6)

$$\theta = 2\pi f_c \frac{\mathrm{dsin}\psi}{c} \tag{6}$$

where  $I_k$  and  $Q_k$  are the downconverted signals from the kth element,  $I'_k$  and  $Q'_k$  are the phase-shifted outputs, and the  $\theta$  is a constant phase for a given incident angle  $(\psi)$  and center frequency  $(f_c)$  as represented in (8). Because multiplication in CWM scales the bit stream with a weight  $[\cos(k\theta) \text{ or } \sin(k\theta)]$ it is efficiently implemented with a 5:1 MUX with the bit stream as the MUX select [Fig. 3(b)].

An important advantage of BSP is the reduced number of decimators. As shown in Fig. 2(a), in the DSP approach each antenna element requires a decimator, however, with BSP there is only one decimator per beam [Fig. 2(b)]. This is an advantage because a high-speed decimator requires extensive high-speed addition, which consumes a significant amount of power. It is shown in [8] that the decimation filters consume 87% of the DBF power in a conventional DSP implementation. Thanks to the reduced number of decimators and MUX-based multiplication, the eight-element two-beam digital beamformer

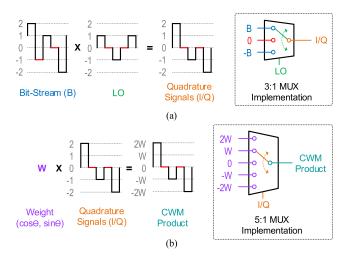

Fig. 4. (a) STF and (b) NTF pole/zero placement of the 4th-order bandpass delta-sigma modulator.

in [8] reduces power consumption by 64% and area by 68% compared to a conventional DSP implementation.

## B. Interleaved Bit Stream Processing Digital Beamformer

The ADC in this paper digitizes the received signals at 4 GS/s for a 100 MHz bandwidth. This also requires the digital circuitry to run at 4 GHz, which is challenging for the BSP MUX logic and especially challenging for the decimators. While the adders in the decimators have input bit widths more than 20-bit, 40 nm CMOS can only perform an 8-10 bit addition in one clock cycle with 40 ps of setup and hold time [10]. To address this challenge, we introduce IL-BSP to halve the clock rate and reduce both power and area significantly.

IL-BSP performs a two-stage decimation with an initial decimation by two at the digital downconversion to reduce the subsequent digital processing rate to 2 GHz. As we will see, this initial decimation by two is very efficient because it takes advantage of the nulls in the noise transfer of the bandpass modulator and also exploits a nearly free two-stage cascaded integrated comb (CIC) filter in the digital downconversion to baseband I and Q signals. After this  $2 \times$  decimation, CWM, summation and final decimation of the beam signals run at 2 GHz.

The initial decimation by two takes advantage of the fortuitous aliasing of noise shaping nulls in the bandpass modulator. For bandpass modulators, the center frequency is chosen to be one-fourth of the sampling frequency to facilitate efficient digital downconversion. With this ratio of center and sampling frequencies, the sampled LO waveforms can be represented as -1, 0, and 1, so that DDC can be implemented with simple MUX.

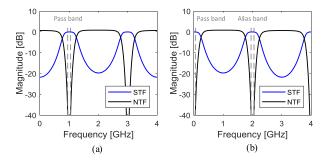

To understand the decimation process, we first consider the noise transfer function (NTF) of the bandpass modulator and the corresponding downmixed NTF. Fig. 4 shows the pole and zero placements for the 4th-order bandpass modulator in this paper. Because the NTF zeros of the bandpass modulator occur in complex conjugate pairs, the NTF of the 4th-order bandpass modulator has two zeros at  $1/4 F_s$  and two more zeros at  $3/4 F_s$ [Fig. 4(b)] [11]. Therefore, the 4th-order bandpass modulator shapes quantization noise from 1/4  $F_s$  and 3/4  $F_s$  with a -40 dB/decade slope, as shown in Fig. 5(a). Downmixing of the bandpass NTF with the 1/4  $F_s$  LO leads to the NTF

Fig. 5. Frequency domain representation of (a) quantization noise from the 4th-order bandpass  $\Delta \Sigma$ , and (b) after downmixing.

in Fig. 5(b), with noise shaping nulls at dc,  $F_s/2$  and  $F_s$ . Downsampling by two to a sampling rate of  $F_s/2$  takes advantage of the fact that the noise null at  $F_s/2$  aliases onto the signal of interest.

A low-cost two-tap CIC filter takes advantage of the 0s in the LO sequence to further minimize any aliasing artifacts associated with downmixing. This allows the downmixing to baseband I and Q and the downsampling by two to be combined in an elegant way. The transfer function of a 1st-order CIC decimation filter is expressed as follows:

$$H(z) = \frac{1 - z^{-2}}{1 - z^{-1}} = 1 + z^{-1}.$$

(7)

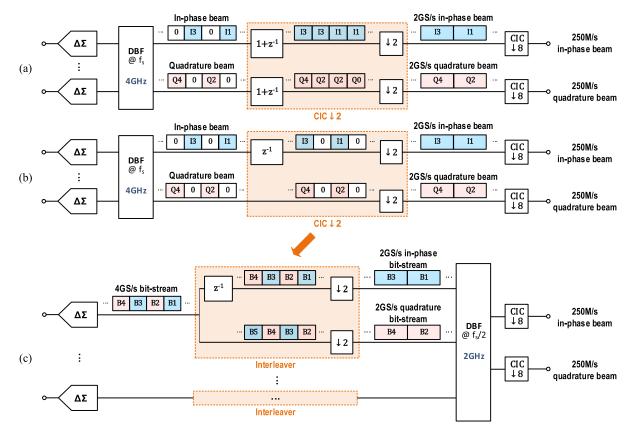

We begin by considering a 1st-order CIC decimation filter and a  $2\times$  decimator placed after the digital downconversion and DBF to generate half rate I and Q signals [Fig. 6(a)]. Because every other LO value is always zero [see Fig. 3(a)], every other I/Q value and every other I/Q beam value are also zero. Due to these zero values, the CIC filter block  $(1+z^{-1})$  repeats each value twice and the subsequent downsampler simply samples one of these repeated values to produce a 2 GS/s beam. More efficiently, the approach in Fig. 6(b), simplifies the filter and decimator with a digital delay  $(z^{-1})$  to produce the same I/Q beams with reduced circuit complexity.

IL-BSP [Fig. 6(c)] moves the digital delay and the  $2\times$  downsamplers of Fig. 6(b) to the front of the DBF block. The combination of the digital delay and downsamplers acts as an interleaver that outputs the even-numbered data as I, and the odd-numbered data as Q. The interleaver allows the digital beamformer to run at half speed without losing any performance or accuracy (Fig. 7). Removing the zeros means ignoring all zero value LO inputs to the DDC. Therefore, DDC is implemented with a 2:1 MUX, driven by the LO values, simplifying circuit implementation, and reducing power consumption.

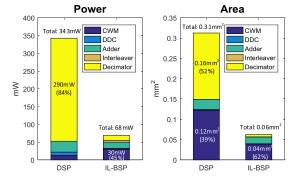

## C. Comparison

Fig. 8 compares power and area of 16-element 4-beam 1 GHz IF digital beamformers implemented with a conventional DSP approach and with the IL-BSP approach. The 16 decimators in DSP consume 84% of the total digital power and occupy 52% of the total area. Although the DDC and CWM in IL-BSP dissipate a comparable amount of power to DDC and CWM in DSP, the IL-BSP decimators only

consume 14 mW, which is far lower than 290 mW for the DSP decimators. Moreover, MUX-based multiplication in IL-BSP reduces the area of CWM by 68%. Consequently, IL-BSP reduces both power and area by 80% compared to a conventional DSP implementation. The entire IL-BSP digital beamformer with 16 elements and 4 beams consumes only 68 mW and occupies 0.0625 mm<sup>2</sup>.

## IV. CONTINUOUS-TIME BANDPASS DELTA-SIGMA MODULATOR

## A. Advantages over Discrete-Time Low-Pass Nyquist ADC

The continuous-time bandpass delta-sigma modulator has several advantages. A continuous-time modulator has inherent anti-alias filtering. As discussed in [12], the NTF of the 4th-order CTBPDSM in Fig. 9 can be expressed as

$$NTF(z) = \frac{1}{1 - L(z)}$$

(8)

where  $L\left(z\right)$  is the discrete-time transfer function from the quantizer output, through the feedback DACs and the resonators, back to the quantizer input. The NTF is expressed in the z-domain because the quantization noise is sampled by the quantizer. The signal transfer function (STF) of the modulator can be expressed as

$$STF(s, z) = \frac{G(s)}{1 - L(z)}$$

(9)

$$= G(s) NTF(z)$$

(10)

where G(s) is the transfer function of the feed-forward path. As  $s = j2\pi f$  and  $z = e^{j2\pi f/f_s}$ , (10) can be rewritten as

$$STF(f) = G(j2\pi f) NTF\left(e^{j2\pi f/f_s}\right). \tag{11}$$

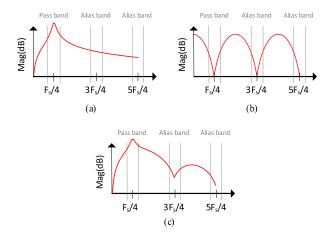

Fig. 10 shows the frequency domain representations of  $G(j2\pi f)$ , NTF  $(e^{j2\pi f/f_s})$ , and STF (f). Although the NTF has zeros in the pass-band [Fig. 10(b)], the poles of the resonators [Fig. 10(a)] cancel the NTF zeros, making a reasonably flat STF gain. On the other hand, the STF gain in the alias bands is much lower because there are no resonator poles [Fig. 10(c)]. Therefore, interference in the alias bands is attenuated, which greatly relaxes anti-alias filtering requirements.

Another advantage of the bandpass modulator approach is that digital mixing does not suffer from I/Q mismatch, mixer noise, dc offset, and flicker noise. Bandpass digitization also halves the number of required ADCs because the quadrature signals share an ADC. On the other hand, two low-pass modulators are required to digitize I and Q signals.

## B. Wide Bandwidth ADC

Emerging standards require relatively wide ADC bandwidths for high data rates. The 4th-order CTBPDSM achieves a 100 MHz bandwidth with a 4 GHz sampling rate and an OSR of 20. Furthermore, small-area and low power consumption are critical as DBF has a large number of ADCs. We reduce power and area with various techniques including: 1) digital array gain; 2) redesign of the feedback DACs; 3) a passive summer; 4) a compact RC-based resonator; and 5) a three-stage nested  $G_m$ -C op-amp.

Fig. 6. (a) Two-stage CIC filter and (b) equivalent implementation of the filter following a BSP DBP block. (c) IL-BSP DBF with an interleaver in front of the DBF block.

Fig. 7. MUX-based (a) digital downconversion and (b) CWM implementation in IL-BSP.

- 1) Digital Array Gain: We exploit the high digital array gain to lower the SNR requirement of the individual ADCs. An advantage of DBF is that it performs highly accurate digital downconversion, and CWM, so that array gain is close to the theoretical limit. This prototype benefits from a near-ideal 11.2 dB array gain, which significantly lowers SNR requirements of the ADCs.

- 2) Elimination of the First Return-to-Zero DAC: We modify the DAC feedback to further save power and area [13]. Conventionally, a continuous-time bandpass modulator requires a

Fig. 8. Power and area comparison between DSP and IL-BSP.

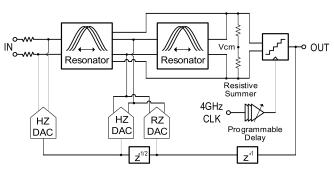

Fig. 9. Fourth-order continuous-time bandpass delta-sigma modulator.

pair of feedback DACs, consisting of a return-to-zero (RZ) DAC and a half-clock-delayed RZ (HZ) DAC for each resonator to perfectly transform a discrete-time modulator into a

Fig. 10. Frequency domain representations of the (a) resonator, (b) noise transfer function, and (c) STF of the CTPBDSM.

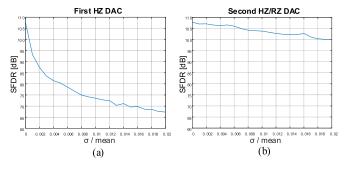

Fig. 11. Effect of mismatch in the (a) first-stage DAC and (b) second-stage DAC on the SFDR of the modulator.

continuous-time modulator. Based on the calculations in [14], the current of the first-stage RZ DAC is made much smaller than that of the first-stage HZ DAC. Due to the small current of the first-stage RZ DAC, proper tuning of the secondstage DACs can remove the need for the first-stage RZ DAC, reducing system noise and power consumption.

The SFDR of the CTPBDSM is limited by the mismatch of the first-stage DAC, as the first resonator attenuates the non-linearity of the second-stage DACs (Fig. 11). The average output current of the first-stage DAC is 70  $\mu$ A, and its standard deviation is 1.4  $\mu$ A. The measured SFDR of the modulator is 66 dB, and the schematic of the first-stage RZ DAC is shown in Fig. 12.

- 3) Passive Summer: A passive summer further reduces power and area. We replace the power hungry active transimpedance amplifier used in [8] with a resistive summer that adds the output current of the first resonator with the output current of the second resonator. Consequently, the CTBPDSM consumes 20% less power and occupies 10% less area.

- 4) High Intermediate Frequency (IF): The single op-ampbased RC resonator in Fig. 13 is used instead of a bulky LC-tank resonator. As discussed in [13], the resonator transfer function T(s) and center frequency  $w_0$  are

$$T(s) = \frac{w_o s}{s^2 + w_o^2}$$

$$w_0 = \frac{1}{2R_p C_p}$$

(12)

$$w_0 = \frac{1}{2R_p C_p} \tag{13}$$

Fig. 12. Schematic of the first-stage RZ DAC.

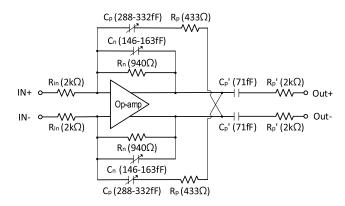

Fig. 13. RC-based single op-amp resonator.

when  $C_p = 2C_n$  and  $R_n = 2R_p$ . As indicated by (13), the center frequency is inversely proportional to  $R_p$  and  $C_p$ . The high IF frequency of 1 GHz, allows the use of smaller resistors and capacitors to reduce the area of the resonators. As a result, the resonator size is only 0.003 mm<sup>2</sup> and the CTBPDSM occupies 0.01 mm<sup>2</sup>. To account for PVT variation, the resonator center frequency is tuned with a 3-bit trim of  $C_p$ and  $C_n$  (Fig. 13).

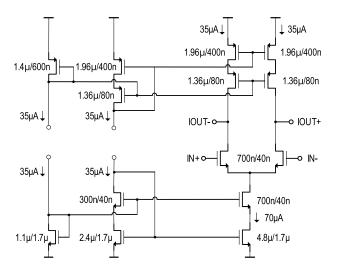

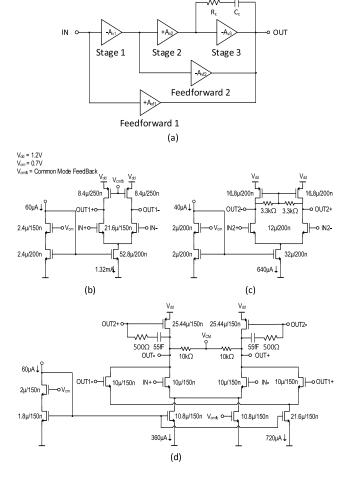

5) Three-Stage Nested Gm-C Op-Amp: Compared to switched-capacitor-based discrete-time modulators, continuous-time modulators have relaxed op-amp bandwidth constraints [12]. We use the three-stage cascaded  $G_m$ -C structure in Fig. 14 which gives a good tradeoff between gain and bandwidth [15]. The first resonator op-amp consumes 5.4 mW and provides 13.22 GHz unity gain bandwidth, 71 dB dc gain with 100 fF load capacitance (i.e., the input capacitance of the second resonator).

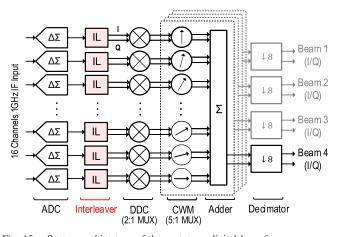

## V. System Architecture

As shown in Fig. 15, the 16-element 100 MHz bandwidth digital beamformer generates four simultaneous beams. The 16 CTBPDSMs digitize the 16 1 GHz IF inputs to create 4 GS/s five-level bit streams. The interleavers have the data rate by interleaving the digitized bitstreams into 2 GS/s quadrature signals. The 2:1 MUX-based DDCs downconvert

Fig. 14. (a) Three-stage nested  $G_m$ -C operational amplifier. Schematic of (b) stage 1, (c) stage 2, and (d) stage 3 with feed-forward amplifiers.

Fig. 15. System architecture of the prototype digital beamformer.

the quadrature signals to base band without adding noise or mismatch. The CWMs shift phase of the downconverted signals with complex weights set by 6-bit registers, resulting in a 0.02° main beam direction resolution. After phase shifting, the adder creates 2 GS/s quadrature beams. Finally, the decimators produce 13-bit 125 MS/s quadrature beams. The prototype digital beamformer has four sets of 16 CWMs, adders, and decimators, to produce four independent simultaneous beams for MIMO.

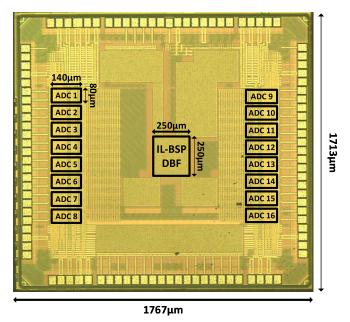

Fig. 16. Die micrograph (0.24 mm<sup>2</sup> of active area in 40 nm CMOS).

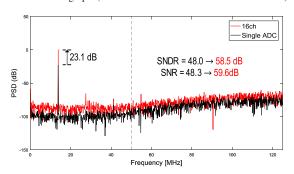

Fig. 17. Measured power spectral density of a single CTBPDSM and overall 16-element beamformer (input frequency: 1.013 GHz).

Fig. 16 shows a die micrograph of the prototype 16-element digital beamformer. The prototype is fabricated in ten-metal 40 nm CMOS and packaged in an 88-lead quad flat no-leads package. It occupies a core area of 0.24 mm<sup>2</sup>, including the 16 CTBPDSMs and the DBF circuitry.

### VI. MEASUREMENTS

### A. CTBPDSM

As shown in Fig. 17 the average measured single ADC signal to noise and distortion ratio (SNDR) over a 100 MHz bandwidth is 48 dB. The overall 16-element array achieves a measured SNDR of 58.5 dB which corresponds to a 10.5 dB improvement from the array. The measured array gain is 11.2 dB, with 59.6 dB SNR from the entire array.

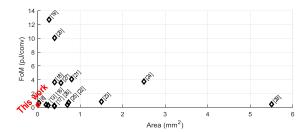

Comparison With State-of-the-Art: Fig. 18 compares the area and Walden FoM [29] of this ADC with other state-of-the-art CTPBDMs. In addition to having the smallest area (0.01 mm<sup>2</sup>) the prototype has one of the best FoMs (365 fJ/conv). Compared to [8], the prototype has 5 times higher bandwidth (100 MHz) and a 4 times higher center frequency (1 GHz), while using 43% less energy per conversion.

Fig. 18. Area and FoM comparison between the CTBPDSM in this paper and other state-of-the-art CTBPDSMs.

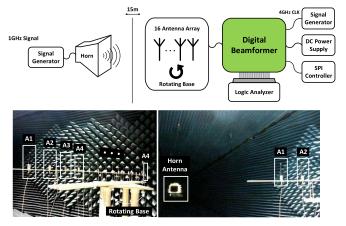

Fig. 19. Anechoic chamber test setup (top) and pictures showing 16 quarterwave whip antennas (A1–A16), spaced at  $\lambda/2$  (15 cm) increments on a rotating base (bottom).

## B. Beam Pattern

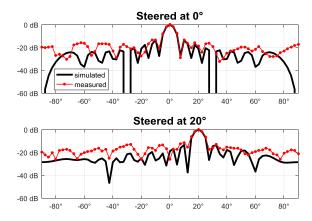

- 1) Wireless Measurements: The resistive input and continuous-time operation allows the prototype device to be directly connected to a linear array of 16 quarter-wave whip antennas, spaced at  $\lambda/2$  increments, without external LNAs. The 16-element antenna array is placed on a rotating base in an anechoic chamber to measure azimuth beam patterns (Fig. 19). A horn antenna with antenna gain of 15 dBi transmits a 15 dBm 1.006 GHz continuous wave signal from a distance of 15 m. An array of whip antennas each with an antenna gain of 1.3 dBi receives the -25 dBm signal. Beam patterns are measured over incidence angles from  $-90^{\circ}$  to  $90^{\circ}$ with a step size of 2.5°. This wireless test is performed without an RF front end. The RF signal is fed directly into the resistive input of the continuous-time ADCs. The ADC noise figure is 26 dB. Fig. 20 shows the measured beam patterns overlaid on ideal beam patterns in the log domain. The beam patterns are normalized. Ideally, the receiver is expected to achieve 55.4 dB SNR. The outer antennas of the 2.25 m antenna array receive significant echoes because they are outside of the 1 m quite zone of the anechoic chamber, resulting in some discrepancy between the ideal and measured patterns. Moreover, echoes and return loss from the 2-m-long antenna cables also cause measurement errors.

- 2) Wired Measurements: To more accurately measure beam patterns without the non-idealities of the anechoic chamber, we generate an array of 16 poly-phase input 1 GHz signals with 16 high-performance direct digital synthesizers (DDSs) shown in Fig. 21.

Fig. 20. Measured and simulated beam patterns of wireless test for  $0^{\circ}$  and  $20^{\circ}$  steered angles (input frequency:  $1.\bar{0}06$  GHz).

Fig. 21. 16 AD9164 DDS boards generate 16 synchronized 1 GHz signals.

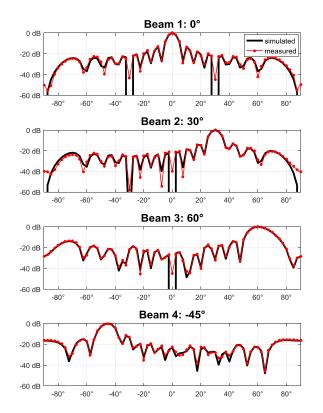

- a) Single main lobe beam pattern: Fig. 22 shows four measured simultaneous independent beam patterns with different incident angles (0 $^{\circ}$ , 30 $^{\circ}$ , 60 $^{\circ}$ , and -45 $^{\circ}$ ). The measured beam patterns are near ideal, with a half-power beam width of  $10^{\circ} - 15^{\circ}$  for a  $+/-60^{\circ}$  incident angle range.

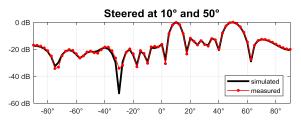

- b) Two main lobes beam pattern: IL-BSP also enables enhanced beam forming with multiple main lobes. As shown in Fig. 23, IL-BSP is programmed to produce a two-main-lobe beam pattern by averaging complex weights for two different single main lobe beam patterns as represented in the following equations:

$$\cos \theta_{1+2} = \frac{\cos \theta_1 + \cos \theta_2}{2}$$

$$\sin \theta_{1+2} = \frac{\sin \theta_1 + \sin \theta_2}{2}.$$

$$(14)$$

$$\sin \theta_{1+2} = \frac{\sin \theta_1 + \sin \theta_2}{2}.\tag{15}$$

Theoretically, ABF can also achieve these beam patterns; however, hardware errors including channel mismatch limit the performance in practice [4]. The prototype digital beam former has measured beam patterns which are almost ideal for two incident angles 10°/50°.

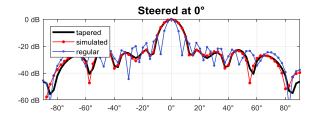

- c) Tapered beam pattern: Fig. 24 depicts measured tapered beam patterns with suppressed side lobes. This adaptive beam forming is performed by applying a Chebyshev window to the complex weights. The measured beam pattern for  $0^{\circ}$  incident angle has side lobes lower than -22.7 dB.

- d) Beam patterns over the bandwidth: Fig. 25 shows the variation of the beam patterns over the +/-50 MHz input bandwidth to measure beam squinting (direction) error.

| TABLE I                                       |  |

|-----------------------------------------------|--|

| BEAMFORMER PERFORMANCE SUMMARY AND COMPARISON |  |

|                        | THIS WORK        | J. Jeong<br>JSSC 2016 [8] | F. Angiolini<br>DATE 2017 [31] | H. Aliakbarian<br>EuCAP 2010 [32] |

|------------------------|------------------|---------------------------|--------------------------------|-----------------------------------|

| Application            | RF Communication | RF Communication          | Ultrasound Imaging             | Satellite                         |

| Integration            | ADC + DDC + DBF  | ADC + DDC + DBF           | DBF                            | DBF                               |

| Center Frequency [GHz] | 1.0              | 0.26                      | 0.004                          | -                                 |

| Bandwidth [MHz]        | 100              | 20                        | -                              | -                                 |

| # of Elements          | 16               | 8                         | 1024                           | 2                                 |

| # of Beams             | 4                | 2                         | 1                              | 1                                 |

| Array SNR [dB]         | 59.6             | -                         | -                              | -                                 |

| Array SNDR [dB]        | 58.5             | 63.3                      | -                              | -                                 |

| SNR improvement [dB]   | 11.2             | -                         | -                              | -                                 |

| SNDR improvement [dB]  | 10.5             | 8.9                       | -                              | -                                 |

| Total Power [mW]       | 312              | 124                       | 5000                           | 500                               |

| DBF Power [mW]         | 68               | 19                        | 5000                           | 500                               |

| Active Area [mm²]      | 0.22             | 0.28                      | -                              | -                                 |

| Technology             | 40nm             | 65nm                      | FPGA                           | FPGA                              |

Fig. 22. Measured and simulated four independent simultaneous beams steered at different angles (input frequency: 994 MHz).

Fig. 23. Beam patterns with two main lobes (input frequency: 1.006 GHz).

The beam squinting error for a beamformer with ideal phase shifters can be approximated as

$$\Delta\Theta = -\frac{\tan\Theta_0}{f_0}\Delta f\tag{16}$$

Fig. 24. Measured tapered beam patterns (input frequency: 1.006 GHz).

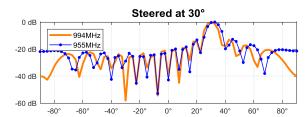

Fig. 25. Measured beam patterns over +/-50 MHz bandwidth (input frequency: 994 and 955 MHz).

where  $\Delta\Theta$  is the squinting error,  $\Theta_0$  is the main beam direction,  $f_0$  is the center frequency, and  $\Delta f$  is the frequency offset of the input signals [30]. When a beamformer is steered at 30°, the theoretical beam squinting error for -45 MHz offcenter frequency is  $1.5^{\circ}$ . The beam pattern in Fig. 25 has a  $2.5^{\circ}$  squinting error, which is the closest number to the theoretical error for a measurement angle step size of  $2.5^{\circ}$ .

e) Performance summary and comparison: Table I compares the digital beamformer prototype IC with state-of-thearts. The digital beamformer in this paper has twice as many beams and elements as [8], which is the most for a published digital beamformer. The prototype consumes 312 mW (16 CTBPDSMs: 244 mW, DBF: 68 mW), and has a 11.2 dB array gain, which is 2.3 dB higher than [8]. It occupies 0.24 mm<sup>2</sup> (16 CTBPDSMs: 0.18 mm<sup>2</sup>, DBF: 0.06 mm<sup>2</sup>) of active area, which is 21% smaller than [8].

## VII. CONCLUSION

This paper expands the complexity and performance of DBF with IL-BSP and compact, efficient bandpass deltasigma ADCs. A digital beamformer with a 1 GHz center

frequency, 100 MHz bandwidth, and 16 elements generates four simultaneous beams. The prototype IC achieves 11.2 dB array gain and consumes only 20 mW/element. IL-BSP consumes 80% less power and occupies 80% less area compared to a conventional DSP implementation. The CTBPDSMs have 5 times higher bandwidth, 4 times higher center frequency, 1/3 area and 43% less energy per conversion than the ADCs in [8]. Thanks to DBF and accurate analog-to-digital conversion, the measured beam patterns, including single main lobe beam, two main lobes beam, and tapered beam, are near ideal.

#### ACKNOWLEDGMENT

The authors would like to thank F. N. Buhler for his kind support. They would like to thank T. Olsson, K. Bunch, B. Epstein, and W. Chappell of DARPA for their advice and support. They would also like to thank Berkeley Design Automation for simulation software and Analog Devices for providing DDS devices.

## REFERENCES

- M. Shafi *et al.*, "5G: A tutorial overview of standards, trials, challenges, deployment, and practice," *IEEE J. Sel. Areas Commun.*, vol. 35, no. 6, pp. 1201–1221, Jun. 2017.

- [2] F. W. Vook, A. Ghosh, and T. A. Thomas, "MIMO and beamforming solutions for 5G technology," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Tampa, FL, USA, Jun. 2014, pp. 1–4.

- [3] O. El Ayach, S. Rajagopal, S. Abu-Surra, Z. Pi, and R. W. Heath, Jr., "Spatially sparse precoding in millimeter wave MIMO systems," *IEEE Trans. Wireless Commun.*, vol. 13, no. 3, pp. 1499–1513, Mar. 2014.

- [4] S. H. Talisa, K. W. O'Haver, T. M. Comberiate, M. D. Sharp, and O. F. Somerlock, "Benefits of digital phased array radars," *Proc. IEEE*, vol. 104, no. 3, pp. 530–543, Mar. 2016.

- [5] A. Lozano and N. Jindal, "Transmit diversity vs. spatial multiplexing in modern MIMO systems," *IEEE Trans. Wireless Commun.*, vol. 9, no. 1, pp. 186–197, Jan. 2010.

- [6] R. W. Heath and A. J. Paulraj, "Switching between diversity and multiplexing in MIMO systems," *IEEE Trans. Commun.*, vol. 53, no. 6, pp. 962–968, Jun. 2005.

- [7] P. K. Bailleul, "A new era in elemental digital beamforming for spaceborne communications phased arrays," *Proc. IEEE*, vol. 104, no. 3, pp. 623–632, Mar. 2016.

- [8] J. Jeong, N. Collins, and M. P. Flynn, "A 260 MHz IF sampling bit-stream processing digital beamformer with an integrated array of continuous-time band-pass ΔΣ modulators," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1168–1176, May 2016.

- [9] S. Jang, J. Jeong, R. Lu, and M. P. Flynn, "A 16-element 4-beam 1 GHz-IF 100 MHz-bandwidth interleaved bit-stream digital beamformer in 40 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Honolulu, HI, USA, Jun. 2017, pp. 124–127.

- [10] I. Levi, O. Bass, A. Kaizerman, A. Belenky, and A. Fish, "High speed dual mode logic carry look ahead adder," in *Proc. IEEE Int. Symp. Circuits Syst.*, Seoul, South Korea, May 2012, pp. 3037–3040.

- [11] R. Schreier and G. C. Temes, "Band-pass and quadrature delta sigma modulation," in *Understanding Delta-Sigma Data Converters*. New York, NY, USA: Wiley, 2005, pp. 141–142.

- [12] R. Schreier and G. C. Temes, "Implementation considerations for ADCs," in *Understanding Delta-Sigma Data Converters*. New York, NY, USA: Wiley, 2005, pp. 205–218.

- [13] H. Chae, J. Jeong, G. Manganaro, and M. P. Flynn, "A 12 mW low power continuous-time bandpass  $\Delta\Sigma$  modulator with 58 dB SNDR and 24 MHz bandwidth at 200 MHz IF," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 405–415, Feb. 2014.

- [14] O. Shoaei and W. M. Snelgrove, "A multi-feedback design for LC bandpass delta-sigma modulators," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, vol. 1. Apr./May 1995, pp. 171–174.

- [15] K. N. Leung and P. K. T. Mok, "Analysis of multistage amplifier-frequency compensation," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 48, no. 9, pp. 1041–1056, Sep. 2001.

- [16] H. Chae and M. P. Flynn, "A 69 dB SNDR, 25 MHz BW, 800 MS/s continuous-time bandpass ΔΣ modulator using a duty-cycle-controlled DAC for low power and reconfigurability," *IEEE J. Solid-State Circuits*, vol. 51, no. 3, pp. 649–659, Mar. 2016.

- [17] J. Harrison, M. Nesselroth, R. Mamuad, A. Behzad, A. Adams, and S. Avery, "An LC bandpass ΔΣ ADC with 70 dB SNDR over 20 MHz bandwidth using CMOS DACs," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2012, pp. 146–148.

- [18] J. Ryckaert, A. Geis, L. Bos, G. Van der Plas, and J. Craninckx, "A 6.1 GS/s 52.8 mW 43 dB DR 80 MHz bandwidth 2.4 GHz RF bandpass ΔΣ ADC in 40 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Anaheim, CA, USA, May 2010, pp. 443–446.

- [19] N. Beilleau, H. Aboushady, F. Montaudon, and A. Cathelin, "A 1.3 V 26 mW 3.2GS/s undersampled LC bandpass Σ Δ ADC for a SDR ISM-band receiver in 130 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Boston, MA, USA, Jun. 2009, pp. 383–386.

- [20] E. Martens et al., "RF-to-baseband digitization in 40 nm CMOS with RF bandpass ΔΣ modulator and polyphase decimation filter," IEEE J. Solid-State Circuits, vol. 47, no. 4, pp. 990–1002, Apr. 2012.

- [21] J. Ryckaert et al., "A 2.4 GHz low-power sixth-order RF bandpass ΔΣ converter in CMOS," IEEE J. Solid-State Circuits, vol. 44, no. 11, pp. 2873–2880, Nov. 2009.

- [22] J. Zhang, Z. Zhang, Y. Xu, Y. Sun, and B. Chi, "A 54.4-mW 4<sup>th</sup>-order quadrature bandpass CT ΣΔ modulator with 33-MHz BW and 10-bit ENOB for a GNSS receiver," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Phoenix, AZ, USA, May 2015, pp. 343–346.

- [23] C.-Y. Ho, W.-S. Chan, Y.-Y. Lin, and T.-H. Lin, "A quadrature bandpass continuous-time delta-sigma modulator for a tri-mode GSM-EDGE/UMTS/DVB-T receiver," *IEEE J. Solid-State Circuits*, vol. 46, no. 11, pp. 2571–2582, Nov. 2011.

- [24] C.-Y. Lu, J. F. Silva-Rivas, P. Kode, J. Silva-Martinez, and S. Hoyos, "A sixth-order 200 MHz IF bandpass sigma-delta modulator with Over 68 dB SNDR in 10 MHz bandwidth," *IEEE J. Solid-State Circuits*, vol. 45, no. 6, pp. 1122–1136, Jun. 2010.

- [25] S.-B. Kim, S. Joeres, R. Wunderlich, and S. Heinen, "A 2.7 mW, 90.3 dB DR continuous-time quadrature bandpass sigma-delta modulator for GSM/EDGE low-IF receiver in 0.25 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 3, pp. 891–900, Mar. 2009.

- [26] Y. Xu, Z. Zhang, B. Chi, N. Qi, H. Cai, and Z. Wang, "A 5-/20-MHz BW reconfigurable quadrature bandpass CT ΔΣ ADC with antipolesplitting Opamp and digital I/Q calibration," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 1, pp. 243–255, Jan. 2016.

- [27] P. M. Chopp and A. A. Hamoui, "A 1-V 13-mW single-path frequency-translating ΔΣ modulator with 55-dB SNDR and 4-MHz bandwidth at 225 MHz," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 473–486, Feb. 2013.

- [28] H. Shibata *et al.*, "A DC-to-1 GHz tunable RF  $\Delta\Sigma$  ADC achieving DR= 74 dB and BW= 150 MHz at  $f_0=450$  MHz using 550 mW," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2888–2897, Dec. 2012.

- [29] R. H. Walden, "Analog-to-digital converter survey and analysis," *IEEE J. Sel. Areas Commun.*, vol. 17, no. 4, pp. 539–550, Apr. 1999.

- [30] S. K. Garakoui, E. A. M. Klumperink, B. Nauta, and F. E. van Vliet, "Phased-array antenna beam squinting related to frequency dependency of delay circuits," in *Proc. 41st Eur. Microw. Conf.*, Manchester, U.K., 2011, pp. 1304–1307.

- [31] F. Angiolini et al., "1024-channel 3D ultrasound digital beamformer in a single 5W FPGA," in Proc. Design, Autom. Test Eur. Conf. Exhib. (DATE), Lausanne, Switzerland, Mar. 2017, pp. 1225–1228.

- [32] H. Aliakbarian, V. Volski, E. van der Westhuizen, R. Wolhuter, and G. A. E. Vandenbosch, "Analogue versus digital for baseband beam steerable array used for LEO satellite applications," in *Proc. 4th Eur. Conf. Antennas Propag.*, Barcelona, Spain, Apr. 2010, pp. 1–4.

Sunmin Jang (S'14) was born in Seoul, South Korea, in 1987. He received the B.S. degree in electrical engineering from Seoul National University, Seoul, in 2013, the M.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015, where he is currently pursuing the Ph.D. degree focusing on digital beamformers.

Mr. Jang was a recipient of the Jeongsong Scholarship in 2013, and a Samsung Scholarship in 2015.

**Jaehun Jeong** (S'11–M'15) received the B.S. degree in electrical engineering from Seoul National University, Seoul, South Korea, in 2006, and the M.S. and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2011 and 2015, respectively.

In 2015, he joined Broadcom Corporation, Irvine, CA, USA.

Dr. Jeong was a recipient of the scholarship from the Korea Foundation for Advanced Studies in 2009.

Rundao Lu (S'17) received the B.E. degree in electronic science and technology from Xi'an Jiaotong University, Xi'an, China, in 2013, and the M.E. degree in integrated circuit engineering from Shanghai Jiao Tong University, Shanghai, China, in 2016. He is currently pursuing the Ph.D. degree with the University of Michigan, Ann Arbor, MI, USA.

His current research interests include RF and mixed-signal IC designs.

**Michael P. Flynn** (M'95–SM'98–F'15) received the Ph.D. degree from Carnegie Mellon University, Pittsburgh, PA, USA, in 1995.

From 1988 to 1991, he was with the National Microelectronics Research Center, Cork, Ireland. From 1993 to 1995, he was with the National Semiconductor, Santa Clara, CA, USA. From 1995 to 1997, he was with Texas Instruments, Dallas, TX, USA, as a Member of Technical Staff. From 1997 to 2001, he was with Parthus Technologies, Cork, Ireland. In 2001, he joined the University of Michigan,

Ann Arbor, MI, USA, where he is currently a Professor. His current research interests include RF circuits, data conversion, and serial transceivers and biomedical systems.

Dr. Flynn is a 2008 Guggenheim Fellow. He was a recipient of the 2016 University of Michigan Faculty Achievement Award, the 2011 Education Excellence Award, the 2010 College of Engineering Ted Kennedy Family Team Excellence Award from the College from Engineering, University of Michigan, the 2005 and 2006 Outstanding Achievement Award from the Department of Electrical Engineering and Computer Science at the University of Michigan, the NSF Early Career Award, in 2004, and the 1992 and 1993 IEEE Solid-State Circuits Pre-doctoral Fellowship. He was the Editor-in-Chief of the IEEE JOURNAL OF SOLID-STATE CIRCUITS from 2013 to 2016. He is a former Distinguished Lecturer of the IEEE Solid-State Circuits Society. He served as an Associate Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS and of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS. He serves on the Technical Program Committees of the International Solid-State Circuits Conference and the European Solid-State Circuits Conference. He formerly served on the Technical Program Committees the Asian Solid-State Circuits Conference and the Symposium on Very Large Scale Integration